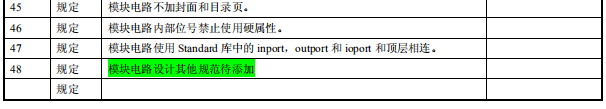

目录

1、原理图制图规范

2、电路设计

2.1、通用要求

2.2、逻辑器件应用

2.3、时钟设计

2.4、保护器件应用

2.5、可编程逻辑器件

2.6、电源设计

2.7、其他应用经验

3、可靠性设计

4、信号完整性/电源完整性设计

5、系统相关设计

6、可生产性设计

7、可生产性设计

7.1、JTAG

7.2、测试点

7.3、电路可测试性

7.4、系统可测试性

本博客将简述中兴通讯股份有限公司在原理图设计中需要注意的一些事项,其中包含了中兴设计开发部积累的大量硬件开发知识和经验,可以作为学习使用。硬件工程师可以学习并掌握检查条目的内容以及对条目的详细说明,学习部门经验。

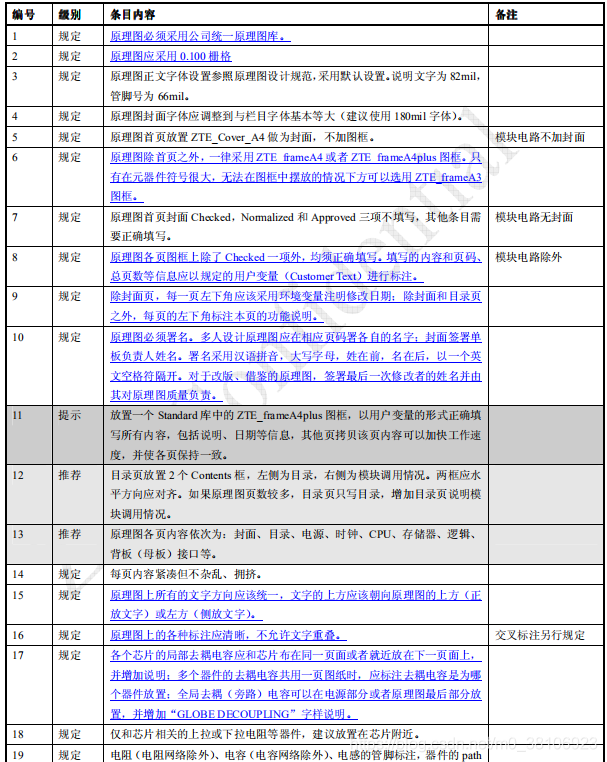

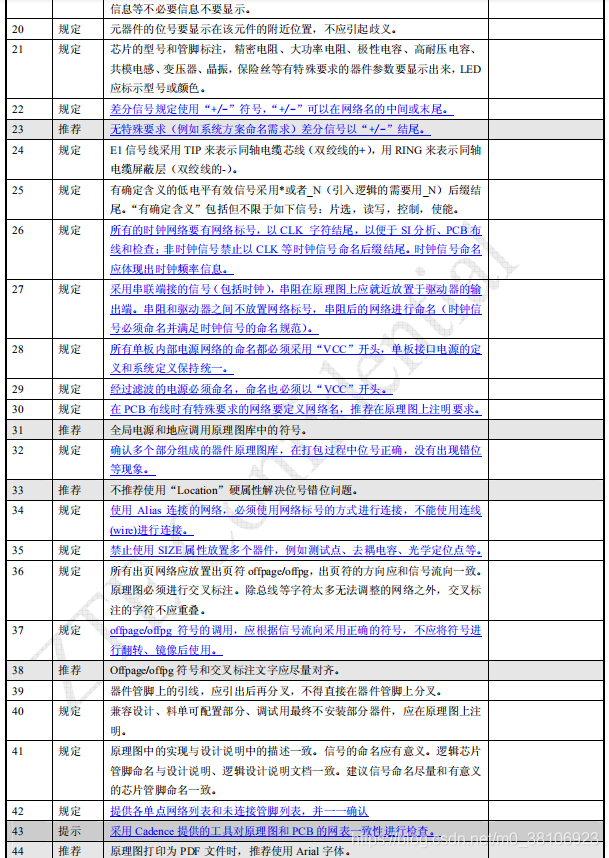

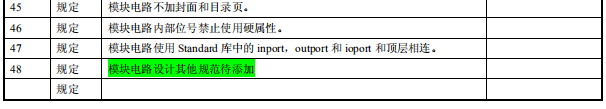

1、原理图制图规范

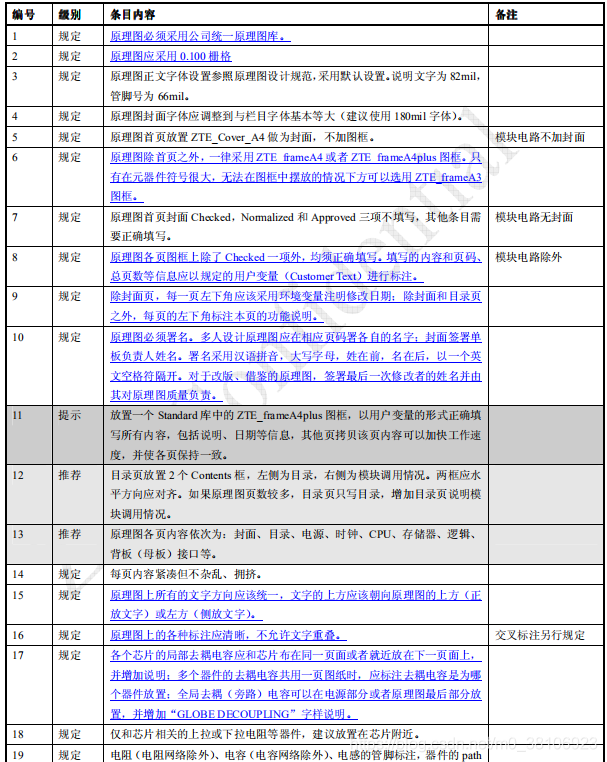

原理图制图规范如下表所示:

详细说明如下所示:

1、原理图必须使用公司统一原理图库?

在原理图设计中,必须采用公司统一原理图库,以保证设计的一致性和打包后封装、料单等结果的一致性。不使用公司统一原理图库造成的连接、封装错误个人承担责任。

注意使 cds.lib 中的路径指向库服务器 eda-svr1 的路径。库服务器每天会和公司统一库服务器同步 2 次确保最新。

在改版设计中尤其要注意这个问题,因为打包时会将部分库备份到本地,可能造成本地库和公司库不一致。

对于历史遗留的未采用统一图库的设计,可以豁免此项检查。但是如果经历改版,必须将原理图库切换至公司统一库,以保证料单的正确性和后续的可维护性。

2、原理图应采用0.100栅格

该栅格设置为一般器件库管脚间距的设置,采用非标准设置的栅格可能会导致其他人员重用原理图时无法对齐。

3、图框大小

部门要求,除非器件符号太大无法在图面内放置,一律采用 A4 幅面的图框进行设计。部门一般均采用 A4 幅面进行打印,在 A3 幅面上绘制的原理图在 A4 幅面纸页上打印后字符无法分辨,难以进行走查、评审。故规定无特殊需要一律采用 A4 幅面图框进行设计。

4、图框上填写的内容和页码、总页数等信息应以用户变量(Customer Text)进行标注

采用用户变量方式标注,可以每页的内容一致,避免出错。如果因为填写错误修改,也只需修改一处即可完成整个原理图的修订,故要求所有原理图的图框信息应采用用户变量进行标注。

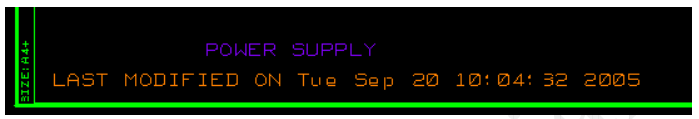

5、每一页左下角标注功能注释和修改日期

如下图所示,采用普通文本标注功能,采用 CON_LAST_MODIFIED 变量标注最后修改日期标注日期。

6、原理图必须署名,多人设计原理图应在相应页码署各自的姓名,封面署单板负责人的姓名

如果一份原理图由多人完成,每个人完成其中一个部分,应在定义环境变量时定义多个环境变量,如 ADRAWN1,ADRAWN2……以此类推。在分配任务时事先约定,在各自完成的部分分开填写相应的用户变量,实现分开署名。封面页的署名为单板负责人的署名。

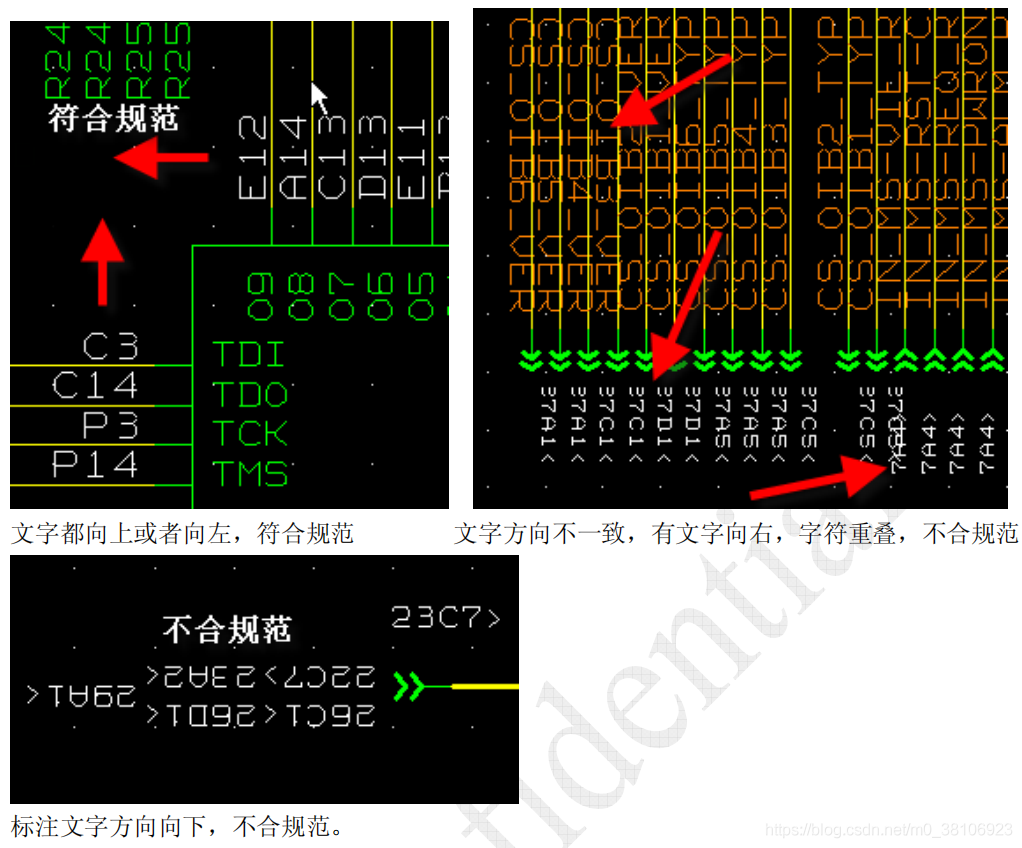

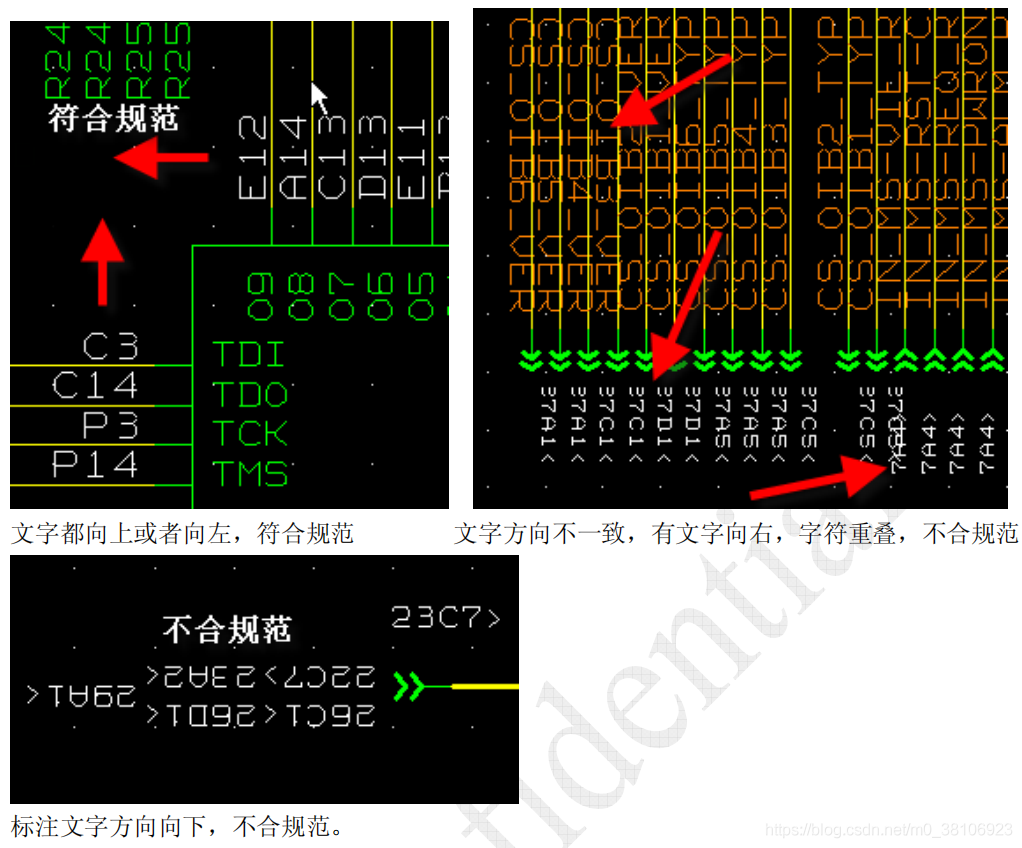

7、原理图上所有的文字方向应该统一,文字的上方应该朝向原理图的上方(正放文字)或左方放文字

8、原理图上的各种标注应清晰,不允许文字重叠

原理图上包括网络名、位好、器件管脚号等各中字符都不允许重叠下面是不符合规范的例子 :

9、去耦电容的放置 ?

去耦电容分为两种:局部去耦和全局去耦。局部去耦目的很明确的布置在芯片附近,为芯片和附近的信号提供信号回流路径和电源去耦。全局电容布置于板上各处。

将去耦电容和器件在原理图上靠近放置,可以有针对性、有计划地添加局部去耦,在布局时应该注意将相应位号的电容摆放在需要去耦的芯片附近。全局去耦电容主要分布在单板上没有去耦电容的部分,以及换层过孔的附近,提供信号回流通路。

10、差分线命名

差分线推荐使用+/-结尾,便于在辨认网络,在布线时添加合适的约束以及信号完整性分析。因为事业部 3G 规范命名中出现信号命名以单板名称为后缀,差分线+/-符号放在中间的情况,为了兼容本规范允许+/-号放在中间。

无特殊情况推荐将+/-符号放在信号名最后。

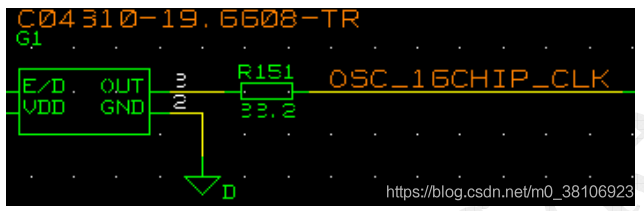

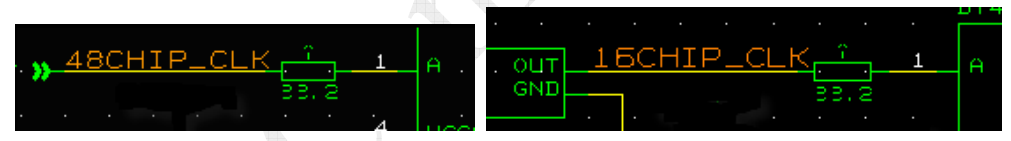

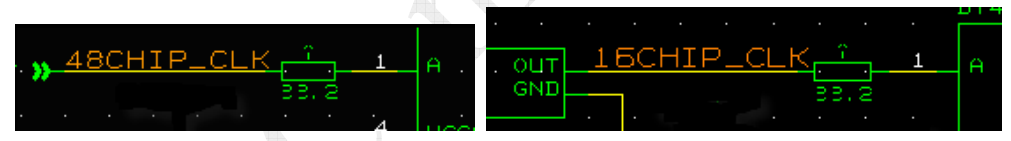

11、时钟信号的命名

为了方便信号完整性分析和布线约束制定,并保证不引起歧义,时钟信号必须以规定的 CLK 后缀结束。其他信号,例如时钟使能信号等,一律禁止以该信号命名后缀结束。时钟信号命名还应体现出时钟频率。根据绘图者的习惯,可以体现出时钟的流向、用途、来源等信息。

例如:FPGA1_8K_CLK,FPGA2_33M_CLK,OIB0_52CHIP_TCLK 都是符合规范的命名。

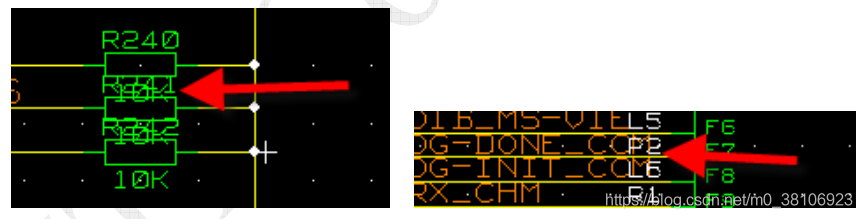

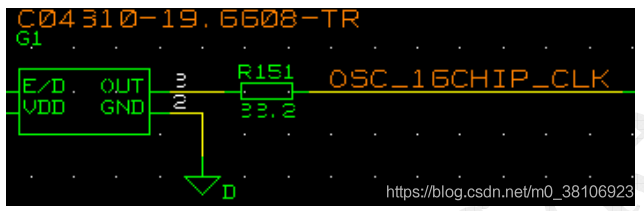

12、串联端接网络的绘制和命名

对于源端端接网络,正确的画法应该是将串阻直接画在驱动器件的输出端,串阻和驱动器件之间的网络可以不进行命名,串阻之后的网络进行命名。如下图所示为一个正确的范例。

如果将串阻放在接收端,或者在串阻之前的信号进行命名,串阻之后的信号不进行命名,都会使得布线的分析和检查困难,甚至会造成串阻被放置在接收端而未被查出的结果,导致信号完整性较差。如下图是不正确的范例:

13、电源及有特殊要求的网络命名 ?

对于电源网络和有特殊要求的网络(例如阻抗控制,电流较大,布线层、过孔数有限制等),必须加以命名,这样在 PCB 进行布线布局时,就可以对相应网络进行特定的约束和检查,确保布线满足设计要求。

对于单板接口电源信号,应该和系统设计保持一致,不强制规范添加 VCC 前缀。但是《PCB 设计说明》中必须明确申明,确保布线符合设计实际需要。

对于一些器件(例如时钟驱动器、锁相环等),其电源单独通过磁珠等进行滤波,往往忘记添加网络标号直接相连,或者添加普通的网络标号。这样的结果很可能导致该网络未按照电源进行布线,走线较细或者走较长线,带来性能上的降低。

14、原理图库多部分构成的器件打包问题

一些器件因为管脚很多,在原理图库中被分成了几个部分,例如部分背板连接器、FPGA、CPU 等。这些器件在绘图过程中很可能被放置在不同的页上。

在打包过程中,很可能出现一个器件的不同部分被分以不同的位号,成为多个器件;以及多个器件位号相互交错的问题。

一般避免此问题有如下方法:

- 对同一个器件的不同部分,设置属性“Group”,定义为同一个组名(例如“FPGA1”);

- 设置位号硬属性“Location”后打包。(反标产生的为“$Location”软属性。)

以上两种方法不能同时使用,否则会出现错误信息(参见 Package XL 手册)。 一般情况下,为了避免打包时或者修改属性时出现其他问题,兼顾模块设计的需要,我们不推荐使 用“Location”指定硬属性的方法解决此问题,建议定义“Group”属性。

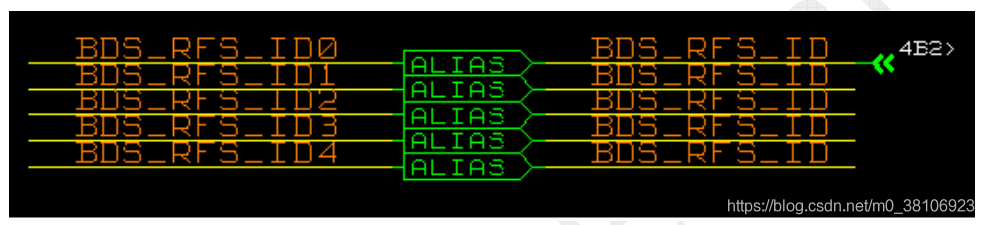

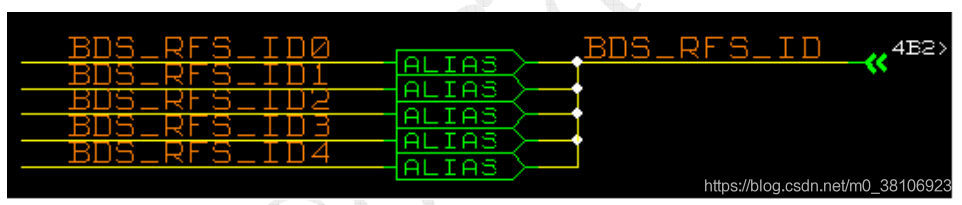

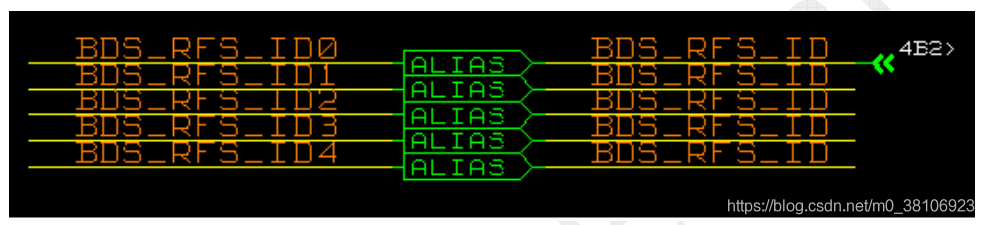

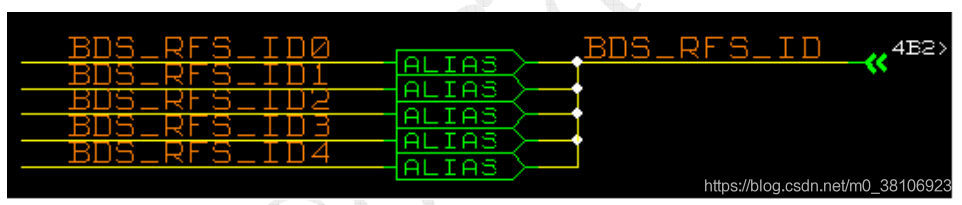

15、Alias 符号的使用

我们有时使用 Alias 来连接网络,以实现同一个物理网络,需要不同名称的场合。例如对于一个网络信号名定义为 PLUG-S,实际和 GNDD 相连,就可以使用 Alias 进行连接,不会发生错误。

使用 Alias 连接的网络,必须使用网络标号的方式进行连接,不能使用连线(wire)进行连接,否则会导致连接失败。

正确的画法为:

错误的画法为:

?两种连接方式看起来完全一样,但是实际上第二种方式在打包时不能形成正确的连接。 ?

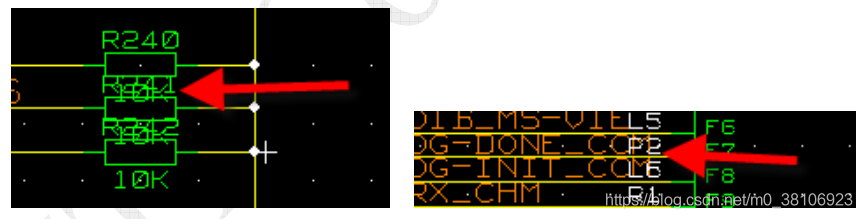

16、禁止使用SIZE 属性放置多个器件

采用定义 SIZE 属性放置多个相同连接关系器件的方法,例如去耦电容、MARK 点等。

采用此种方法虽然方便了原理图绘制,但是导致位号难以控制的问题。当布局布线要求需要调整数量时,很可能出现调整掉已经布局好位号等问题,所以本部门规定,禁止使用 SIZE 放置多个相同连接关系的器件。

17、Offpage/offpg 符号的调用

Offpage 符号在原理图库中一共有六种,如下图所示:

这六种符号分别表示出了输入、输出和双向信号从左右两个方向进入页面。垂直的出页符由水平的出页符翻转实现。需要注意的是出页符在使用中不能通过镜像、翻转的方式作为相反方向的出页符使用,例如将左侧入页符 1 翻转、镜像后作为右侧入页符 4 使用,否则会出现文字位置、方向错误的现象。

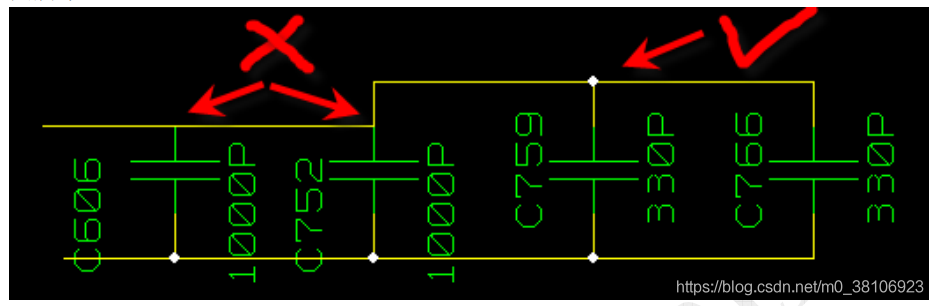

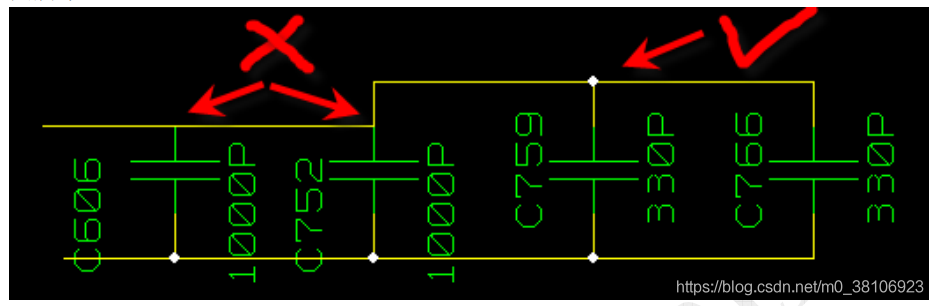

18、器件管脚上的引线,应引出后再分叉 ,不得直接在器件管脚上分叉

在绘图时,如果遇到 T 型的网络,必须将远见引脚引出后连接,不得直接在器件管脚连出分叉, 如下图所示。

采用上图中左侧的方式,在原理图打印后,无法确认网络连接。故不推荐使用。

19、关于单节点网络和浮空管脚的检查

在设计中出现单节点和浮空管脚是很正常的事情,例如单板静电泄放模块中有很多单节点。本条目要求的是对所有的单节点和未连接管脚进行确认,确保没有漏接网络或者遗留未处理的CMOS 输入管脚、器件控制管脚器件控制管脚。

20、采用Cadence提供的工具对原理图和PCB的网表一致性进行检查

?

2、电路设计

2.1、通用要求

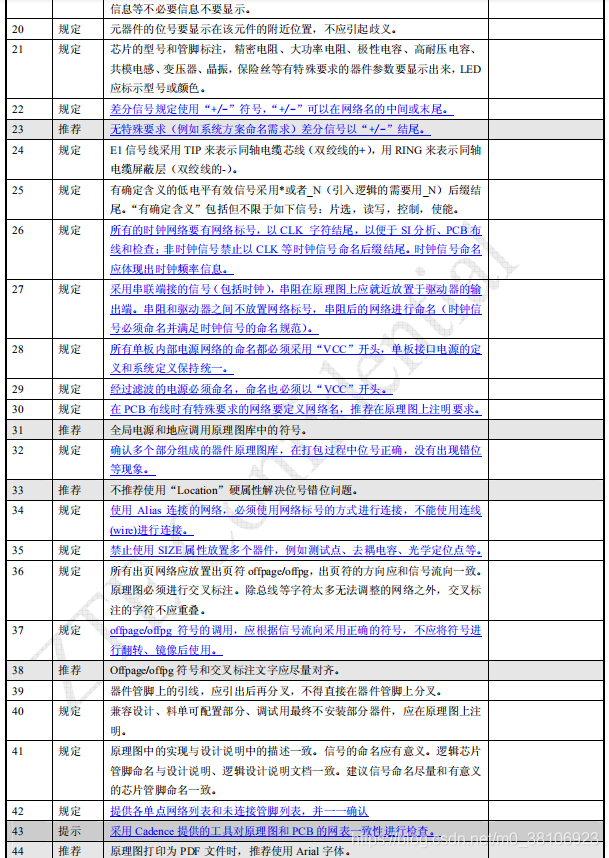

通用要求规范如下表所示:

详细说明如下所示:

1、器件接口电平匹配

器件接口之间的电平应该匹配,尤其要注意不同电压/电平类型逻辑进行接口的场合。

例如我们常用的 LVTTL 信号输入低电平阈值和高电平阈值分别为 0.8V 和 2.0V。虽然器件实际反转电平处于 0.8~2.0V 中间的某一个电压,但是设计必须保障输入电平不会处于两个阈值之间。

对于差分线,要考虑逻辑的共模电压和差分电压范围是否都能够满足要求。 在不同标准、不同电压的逻辑电平进行接口时,尤其要注意这个问题,并避免器件工作在安全工作范围之外。

例如某单板中曾使用 3.3V 的 PCI 时钟驱动器 CDCV304 分发射频时钟,时钟来源于 1 颗 5V 的压控晶体振荡(VCXO),该振荡器为 CMOS 输出。VCXO 的输出电压范围超出了 CDCV304 输入的电压范围,长期工作可能对 CDCV304 的钳位电路或 VCXO 的驱动电路造成损伤。

随着工艺的进步,线宽减小,很多逻辑器件的内置保护电路变得非常脆弱,不能长期承受过应力,器件对过冲等指标也提出了要求。在设计中应予以甄别。

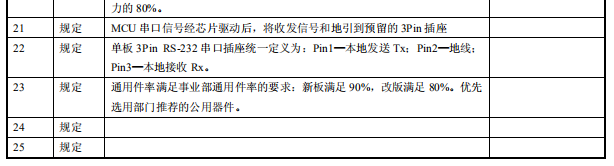

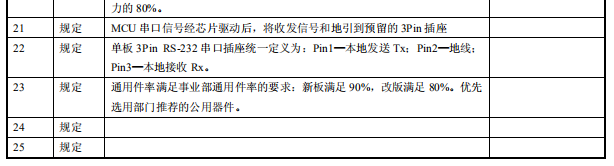

2、PECL-LVPECL 接口

PECL 信号电源电压为 5V,在和 LVPECL 接收器进行接口时直流偏置工作点不满足要求。对于数据流经过直流编码的应用,可以采用交流耦合方式,即在信号线上串联电容隔断直流,两边分别采用上下拉电阻设置工作点。交流耦合电容如直接对单板外部接口,则存在对对方单板输入器件的 ESD 损伤隐患。采用上面提到的,在耦合电容另外一边对地接大电阻防止静电积累是可以的,但要考虑对信号的影响,所以需要对改电路进行实际验证才可以下结论。

对于必须采用直流接口的场合,应采用公司的 3 电阻端接参考设计。电路原理图如下图所示:

3、单板对外接口器件选型必须能够满热拔插要求

在单板对外接口器件选型时,应确保器件可以经受热拔插。对于普通逻辑电平器件,应考虑采用支 持 OE 控制、Ioff、PU3S 的器件。

对于其他器件也应充分考虑器件在电源为 0 的情况下,是否会导致器件损坏、信号线被拉死情况,当单板上电且输入悬空的情况下,是否会出现输出乱码或错误电平、器件损坏等情况,并进行相应处理。

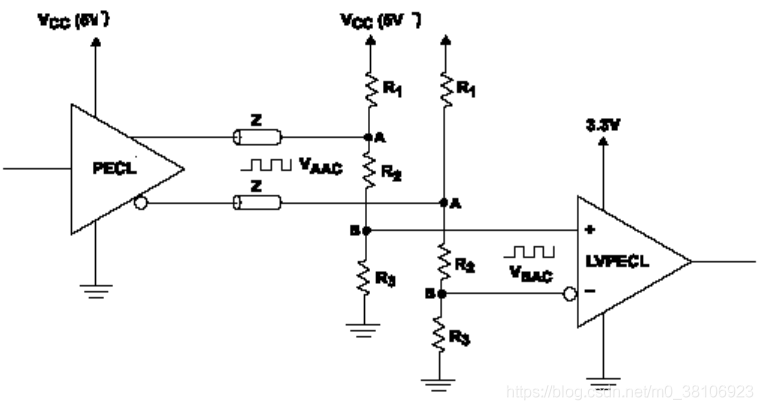

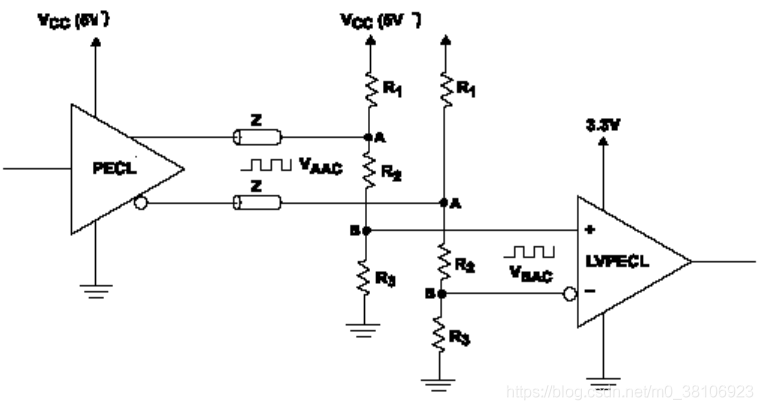

4、对电源有二极管钳位保护的器件

当器件内部存在对电源钳位的二极管时,输入电压高于电源电压(或者在热拔插场合电源电压被关闭、还没有启动),则输入电压会被二极管钳制,对其他信号造成影响,并很可能造成驱动器件或者钳位二极管的过应力损坏。

如果器件的电源没有吸纳电流的能力,且该电源本身电流很小,则输入有可能通过钳位二极管拉高电源电压,造成局部电源过压,对器件造成损坏。

5、差分信号应考虑Failsafe 功能

差分线的 Failsafe 功能包括当驱动器断电,接收器断电,驱动器未连接,差分线开路,差分线短路(或者通过匹配电阻连接)等状况下,器件不应该损坏。更高的要求是当因为上述各种原因,差分线处在中间电平时,接收器应该输出一个固定的状态。接收器输出乱码很可能导致器件的时序不满足要求而 导致状态机跑飞等故障。

我们的 3G 系统中大量使用 MLVDS 器件发放时钟,可以参考 TI 公司 SLLD009 等文档了解 MLVDS器件的 Failsafe 功能。I 型 MLVDS 器件在我们系统应用中,在无驱动状态下会因为干扰而输出乱码,采用 II 型器件可以解决;我们系统中的 RS-485 器件,当接收端接有端接电阻且无驱动的情况下,输出低电平,造成 UART 接收到错误的码,需要进行上拉或下拉处理。

我们系统中 RS-485 总线的处理也是考虑到 Failsafe 功能和器件驱动能力之后综合考虑的结果。

6、了解 CMOS 器件的闩锁现象,选用不易发生闩锁的器件

CMOS 器件的闩锁(Latch-up)现象是由 CMOS 工艺结构所造成的。CMOS 器件在生产过程中,会寄生 PNPN 结构,相当于一个 SCR(Silicon Controlled Rectifier)。当因为电源电压异常、输入电压/输出电压高于电源或者低于地、ESD 放电等情况出现时,就有可能触发闩锁。 当闩锁发生时,器件内部的寄生 SCR 被触发,形成从电源到地的电流直通通路,产生大量热导致 器件烧毁。

一般触发源消失后闩锁仍然保持,只有断电能够退出闩锁状态。为了降低器件发生闩锁的概率,我们在设计中应该理解并选择不易发生闩锁的器件。在一些器件手册上会说明,闩锁性能满足 JESD78 规定的某一级要求,均可作为参考。

?

同时,我们在应用中应该尽量避免触发闩锁的条件,例如:

7、器件工作速率符合设计要求

器件和引入信号的交流特性应该匹配,例如 EPLD 是否支持引入的高速时钟信号以保证逻辑能够正确采样;时钟 BUFFER 是否用来驱动比其所能支持的频率更高的时钟信号等。例如 SN65MLVD200 器件,其数据手册上的速率为 100bps,折算成时钟频率为 50MHz,如果我们用来驱动 60MHz 的信号,虽然可以工作,但是性能不能再得到数据手册上的保证。

8、在满足系统性能要求的情况下,尽量降低信号的速率,采用慢速器件

高速器件主要指信号切换速率高的器件。因为切换速率高对应着工作频率也能增加,所以两者有一定的联系。