前文导读:

计算机组成原理第一章

计算机组成原理第三章

一、概述:

存储器是计算机系统中的记忆设备,用来存放程序和数据。随着计算机的发展,存储器在系统中的低位越来越重要。

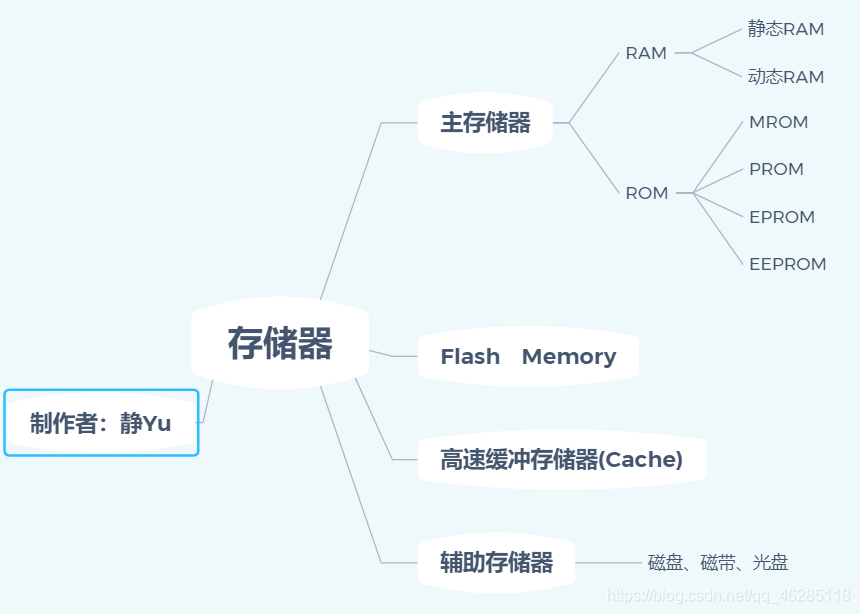

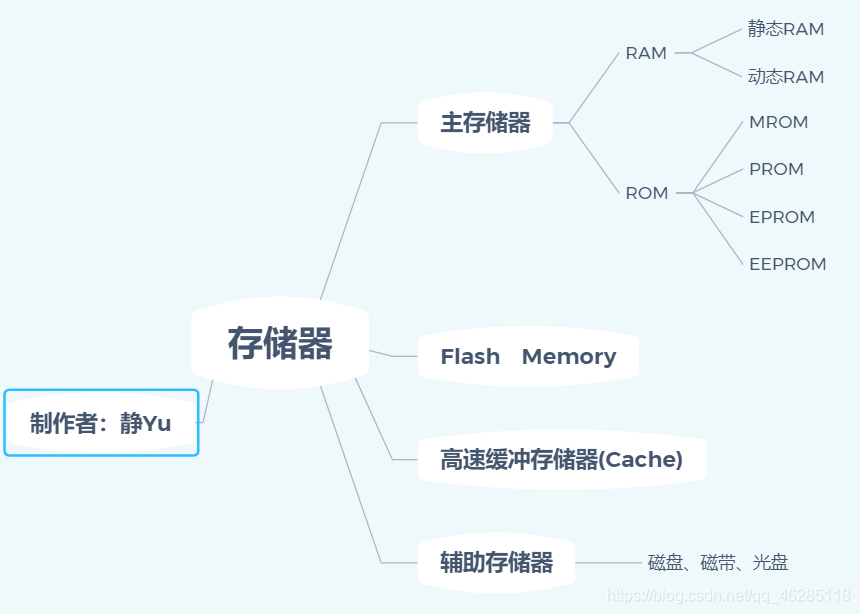

(1)存储器的分类

按存储介质分类

半导体存储器:TTL、MOS

磁表面存储器:磁盘、磁带、磁鼓

磁芯存储器:硬磁材料的环状元件

光盘存储器:激光、磁光

按数据保存方式分类

随机存储器RAM:易失性;包含静态随机存储器、动态随机存储器

只读存储器ROM:非易失性;掩膜型只读存储器(ROM)、可编程只读存储器(PROM)、可擦除可编程只读存储器(EPROM)、电可擦除可编程只读存储器(EEPROM)、闪速存储器(Flash Memory)

按数据存取方式分类

直接访问:内存,访问时间不随访问位置而变化

串行访问:磁带,访问时间随访问位置而变化

部分串行访问:磁盘(寻道直接,等待串行)介于上述二者之间

按在计算机中的作用

主存储器、辅助存储器、高速缓冲存储器

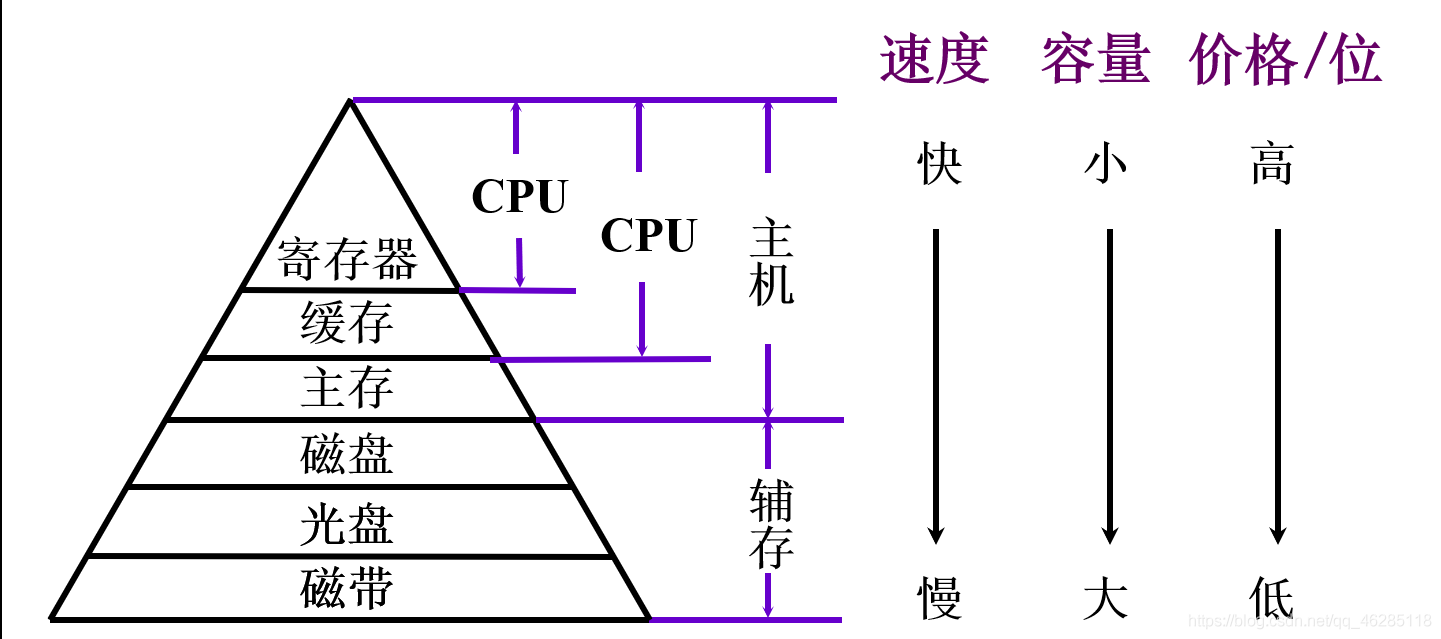

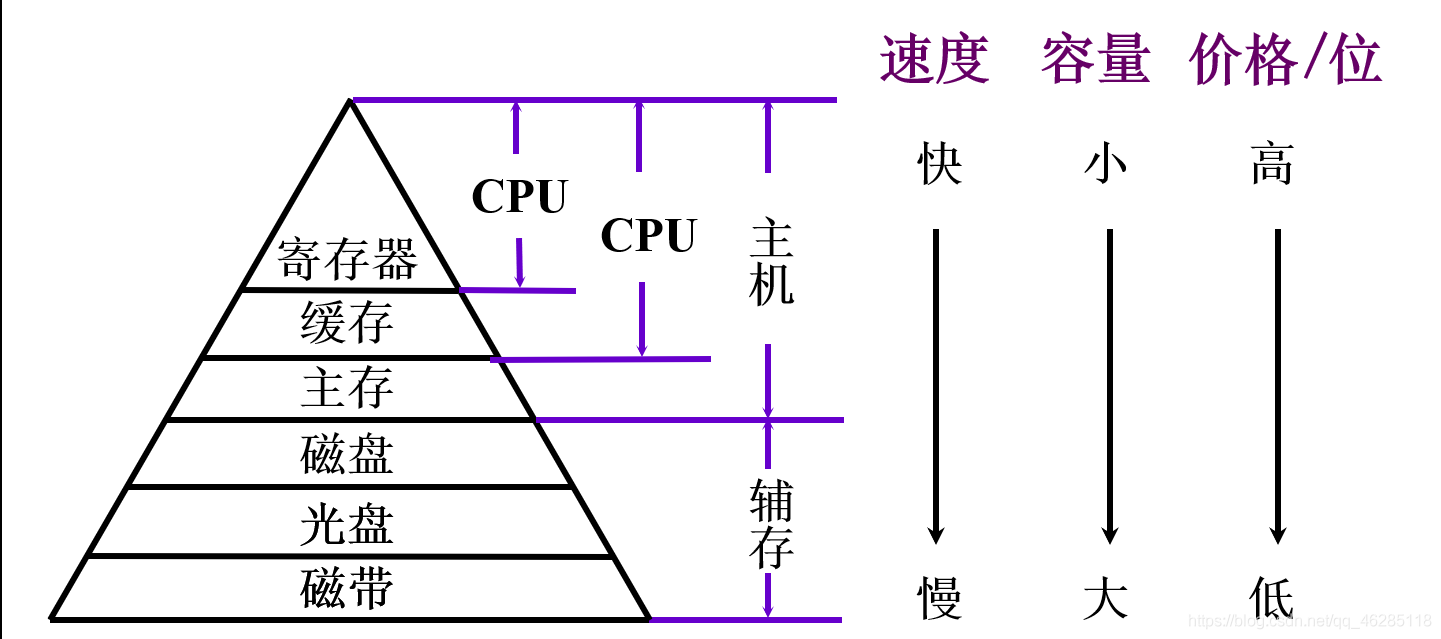

速度:由上到下,由高到低

价格:由上到下,由高到低

容量:由上到下,由低到高

存储器分类总结

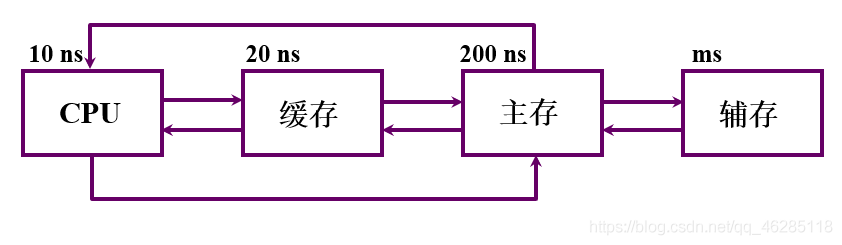

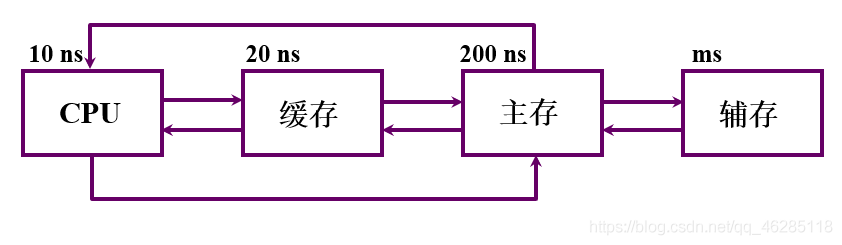

(2)存储器的层次结构

?缓冲――主存层次

主要解决CPU和主存速度不匹配问题,由于缓冲速度较快,将CPU近期要用的信息调入缓存,? ? ? ? CPU可以直接从缓存中获取信息。主存和缓存之间的数据调动是硬件自动完成的,对程序员是透明的。

主存――辅存层次

主要解决存储系统的容量问题,辅存容量大可以存放主存暂时不用的信息。主存和辅存之间的数据调动是由硬件和操作系统共同完成的。

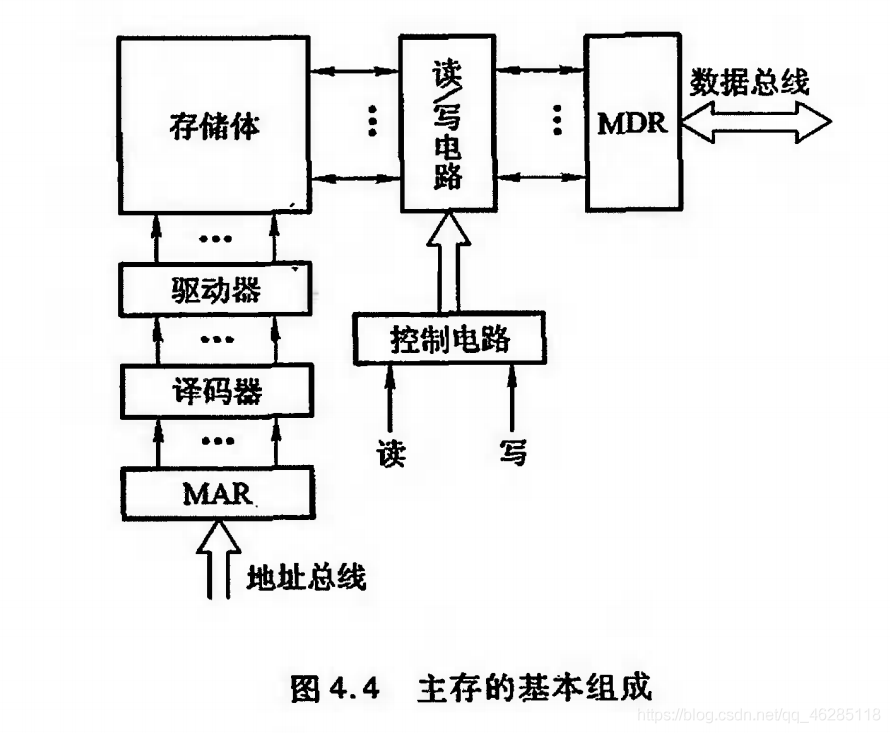

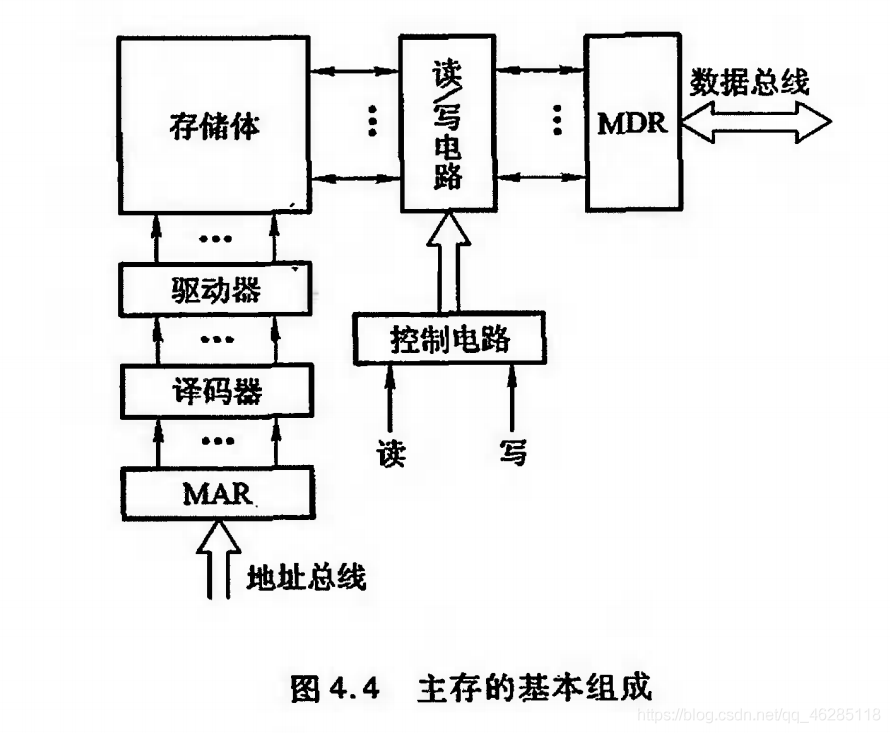

二、主存储器

二、主存储器

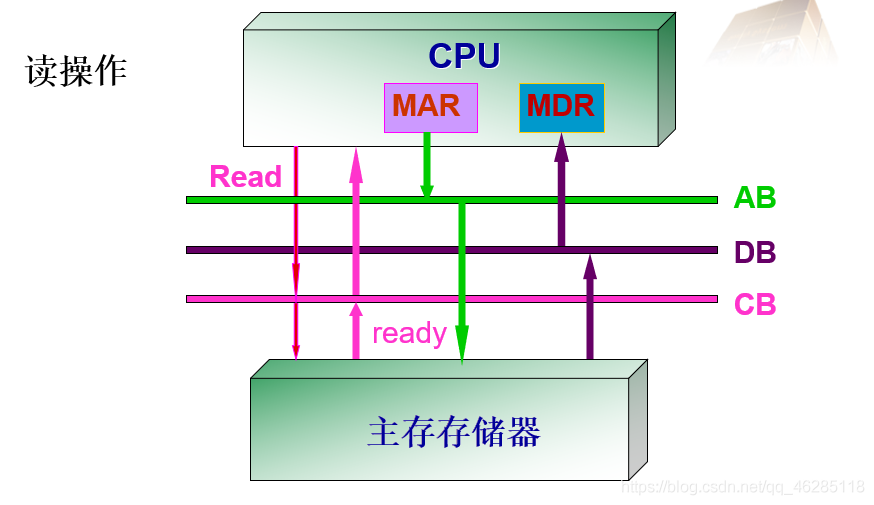

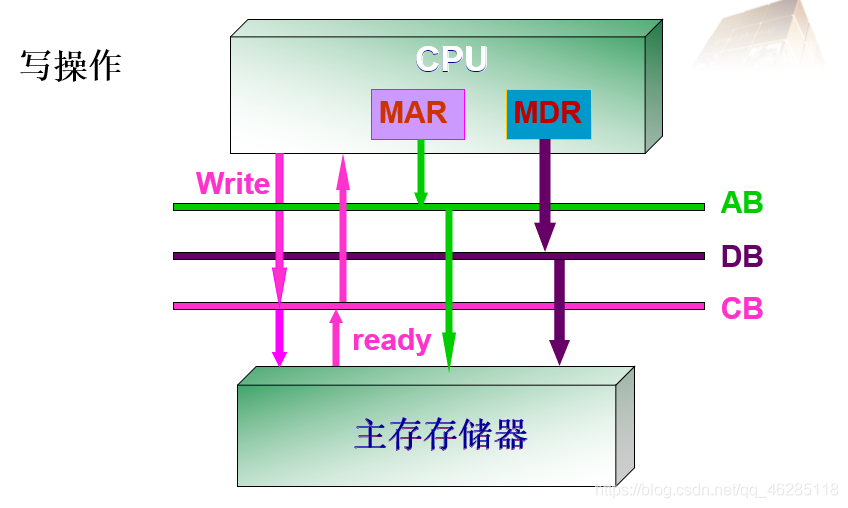

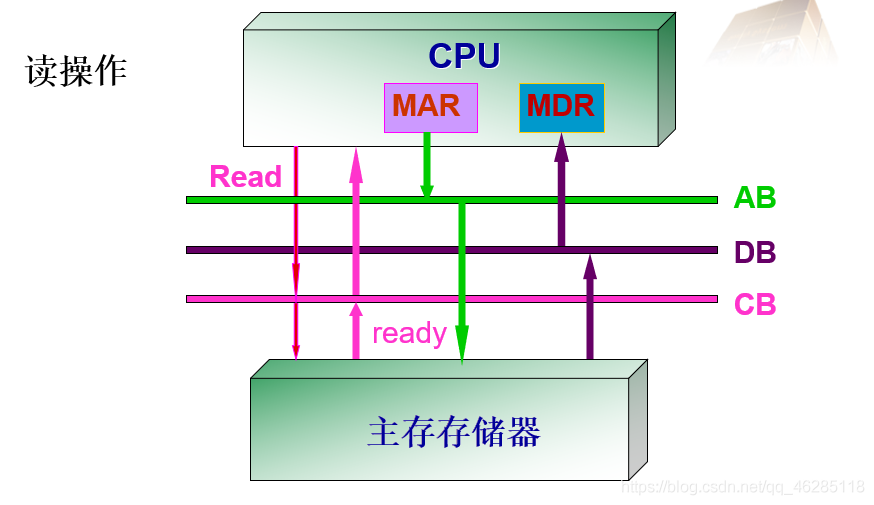

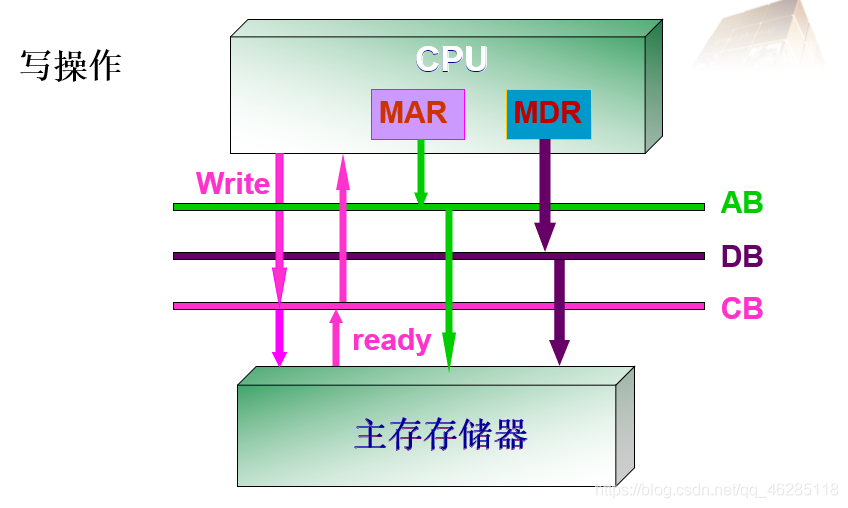

(1)主存和CPU的联系

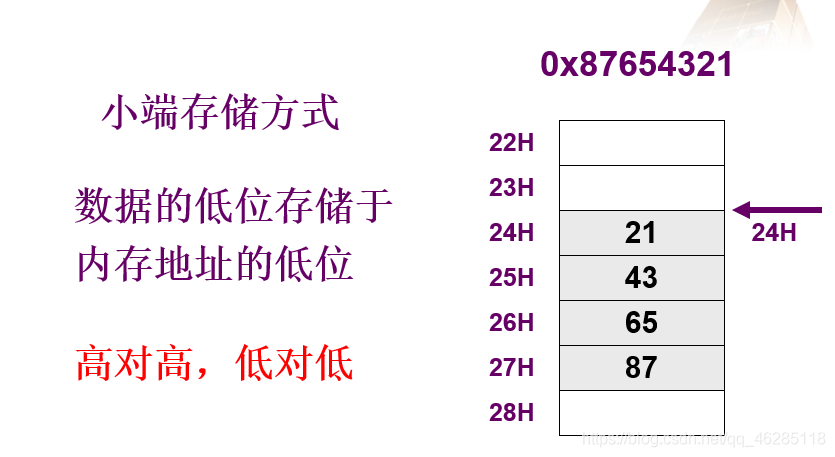

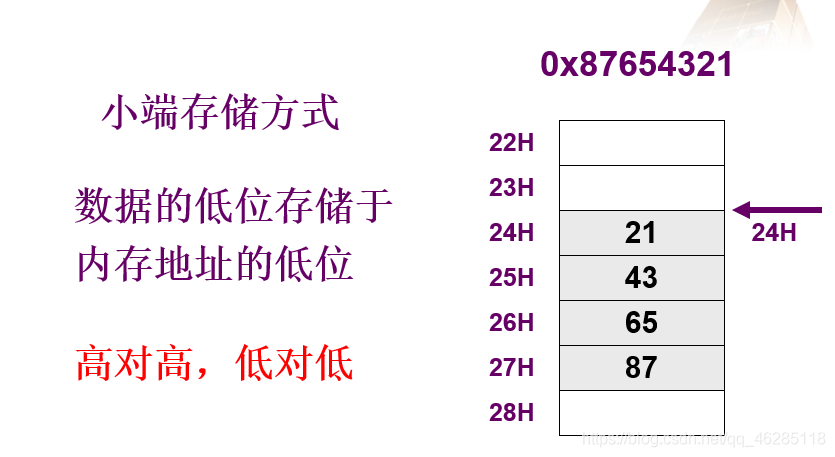

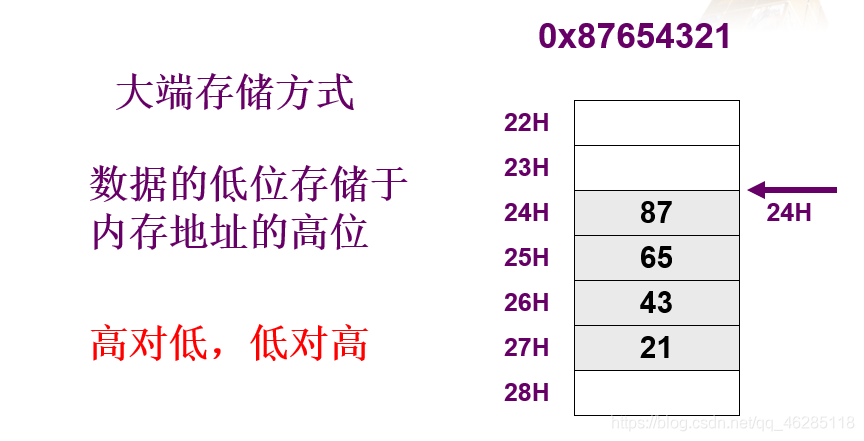

(2) 数据存储模式:大端和小端

?

?

(3)主存的技术指标

主存的主要技术指标是存储容量和存储速度。?

存储容量:存储容量是指能存放二进制代码的总位数。

存储容量=存储单元个数×存储字长

目前计算机存储容量大多以字节数来表示,例如:某机主存的存储容量为256MB,则按字节寻址的地址线位数应对应28位。

存储速度:存储速度是由存取时间和存取周期来表示的。

存取时间又称为存储器的访问时间,是指启动一次存储器操作到完成该操作所需的全部时间。

存取周期进行连续两次独立的存储器操作所需的最小间隔时间,通常・存取周期大于存取时间。

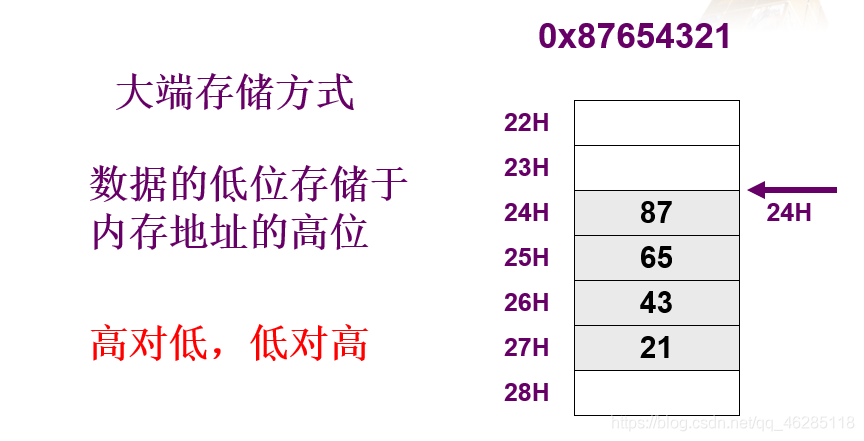

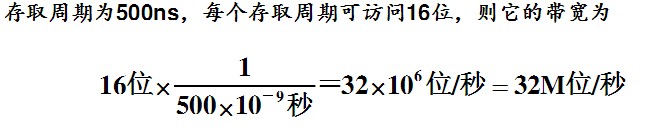

存储器带宽:单位时间内存储器存取的信息量。单位:字节/秒,字/秒,位/秒

例如:存取周期是500ns,每个存取周期可访问16位,则带宽是32M位/秒

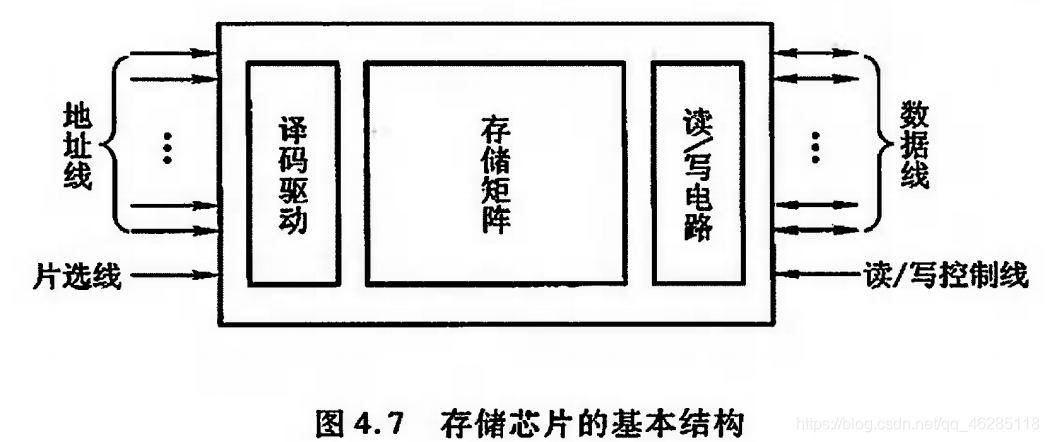

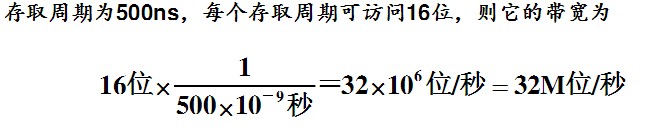

(4)半导体存储芯片简介

(4)半导体存储芯片简介

?

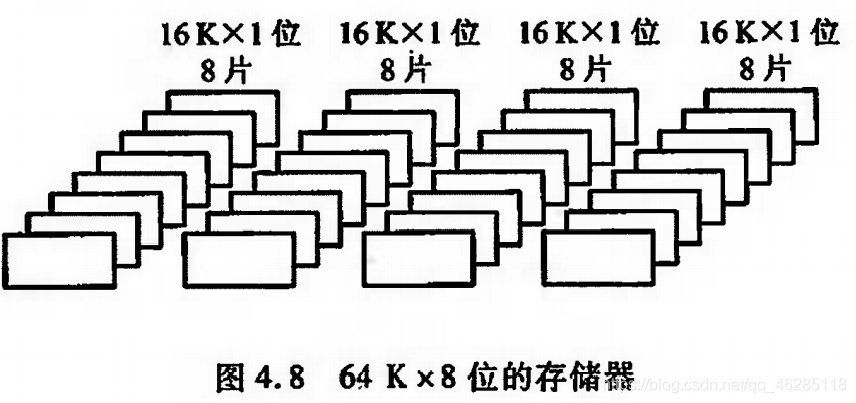

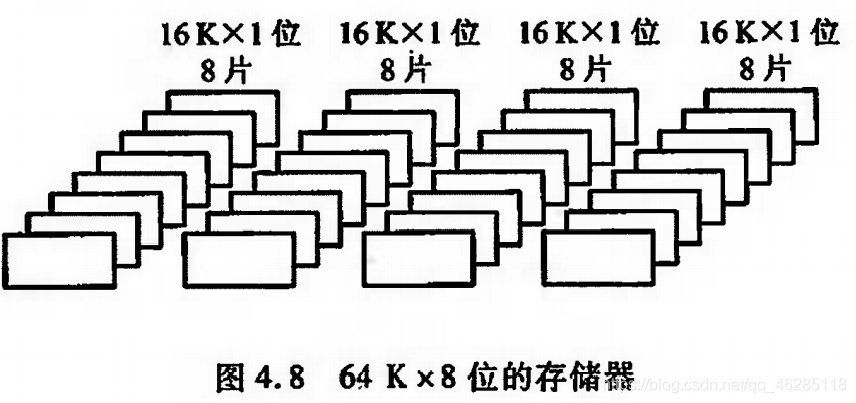

?由于半导体存储器是由许多芯片组成的,为此需用片选信号来确定哪个芯片被选中。例如:一个64K×8位的存储器可由32片16K×1位的存储芯片组成。????????

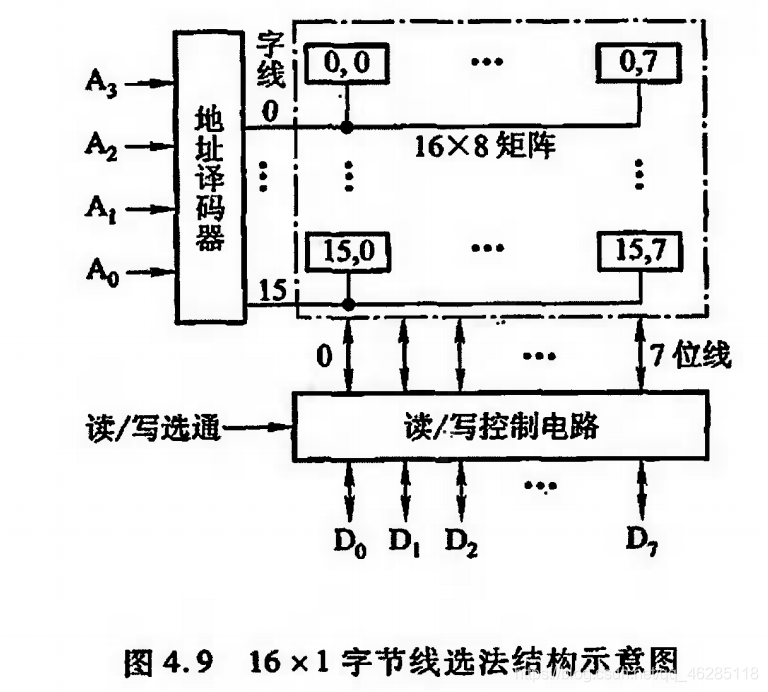

半导体译码驱动:(线选法和重合法)?

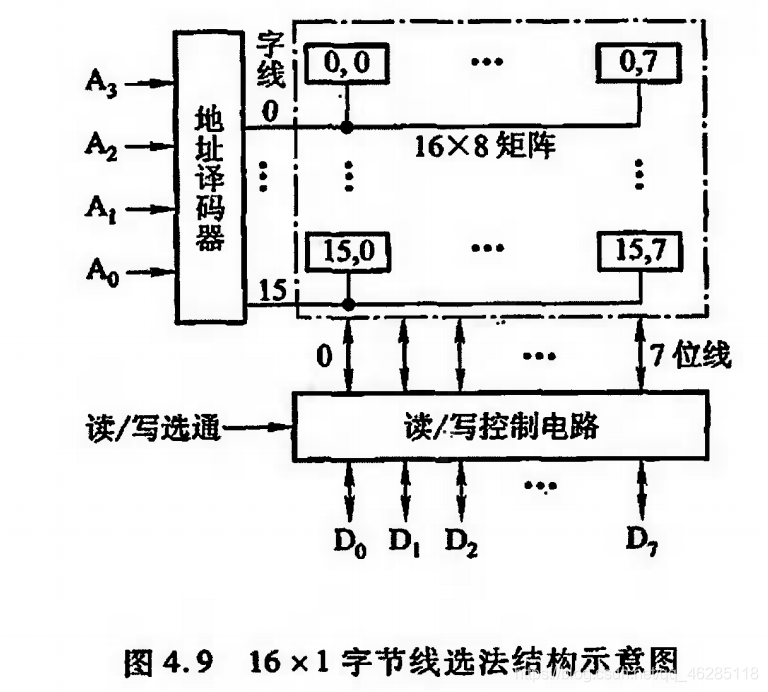

线选法:

一根字选择线直接选中一个存储单元的各位。这种结构方式简单,但只适合容量小的存储芯片。

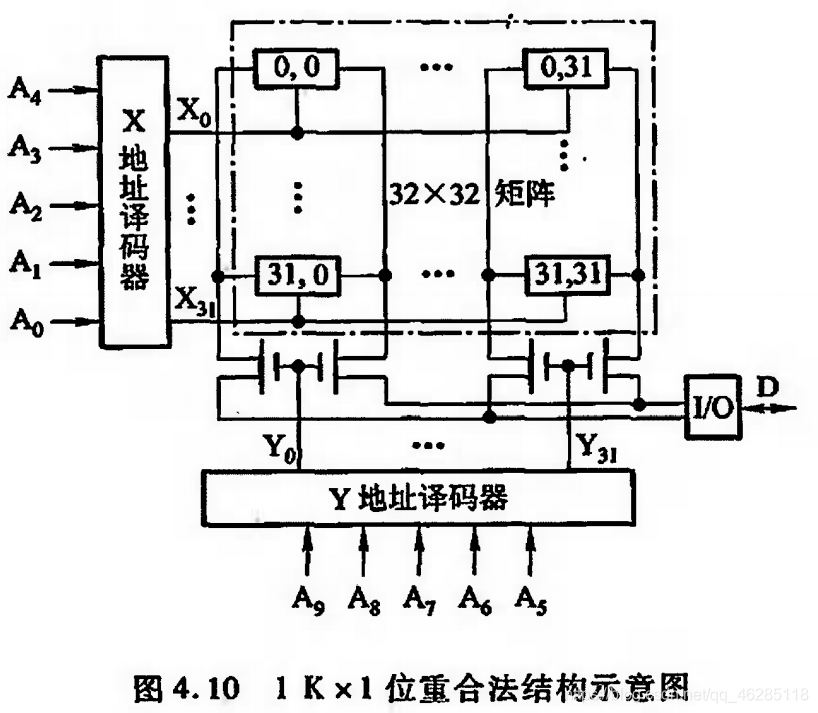

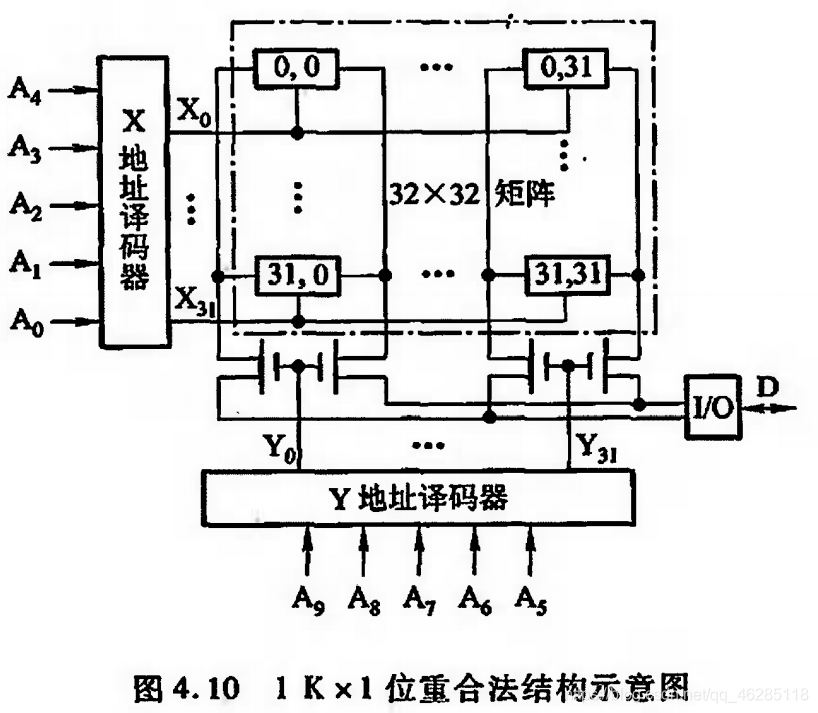

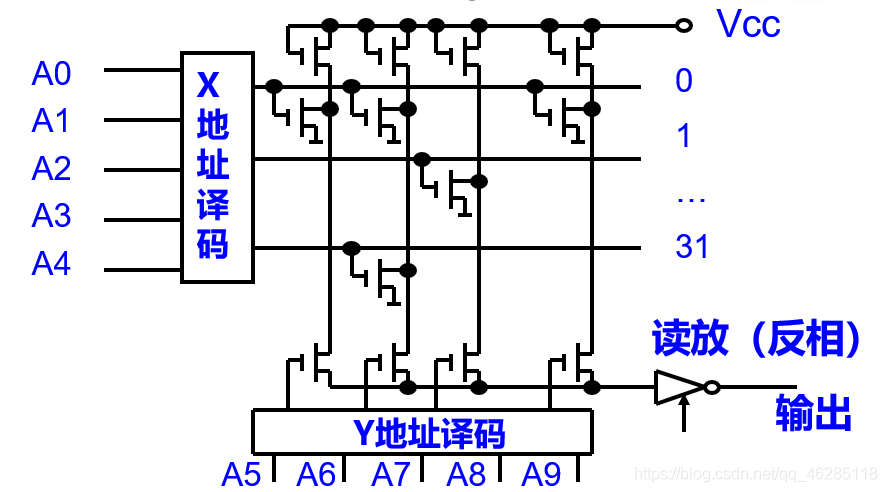

?重合法:

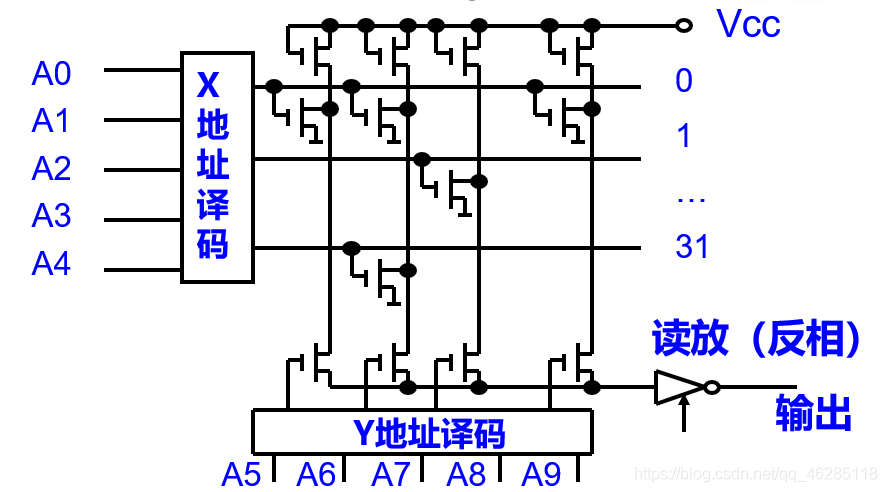

需要X,Y两个方向各32根选择线,构成一个32×32的矩阵。当地址线全为0,译码输出X0和Y0有效,矩阵中第0行,第0列被选中。

(5)随机存取存储器RAM

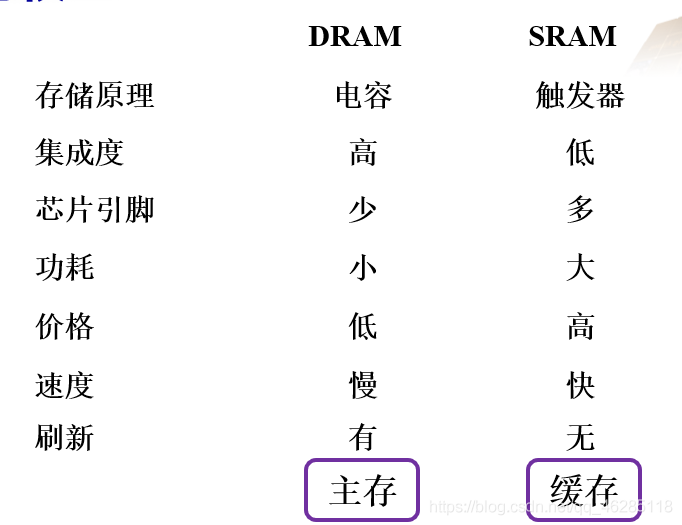

静态随机存储器 :SRAM

动态随机存储器:DRAM

动态RAM的刷新:

动态RAM是利用电容存储电荷的方式来保存信息的,电容很小,很容易漏电,容易造成信息丢失,所以要对动态RAM进行刷新

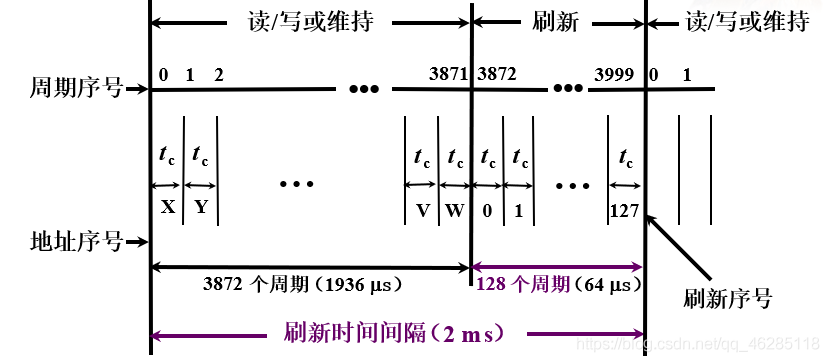

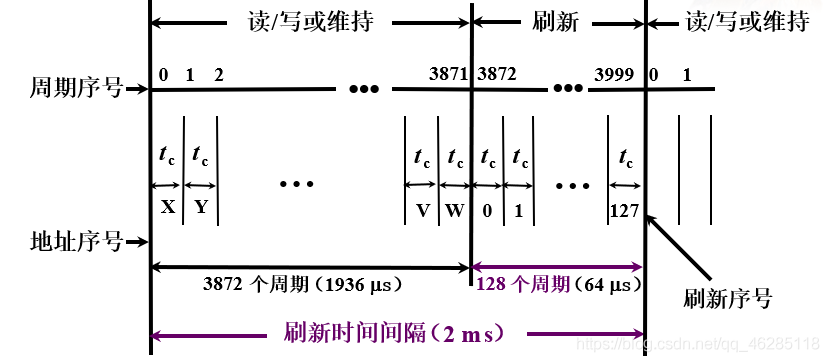

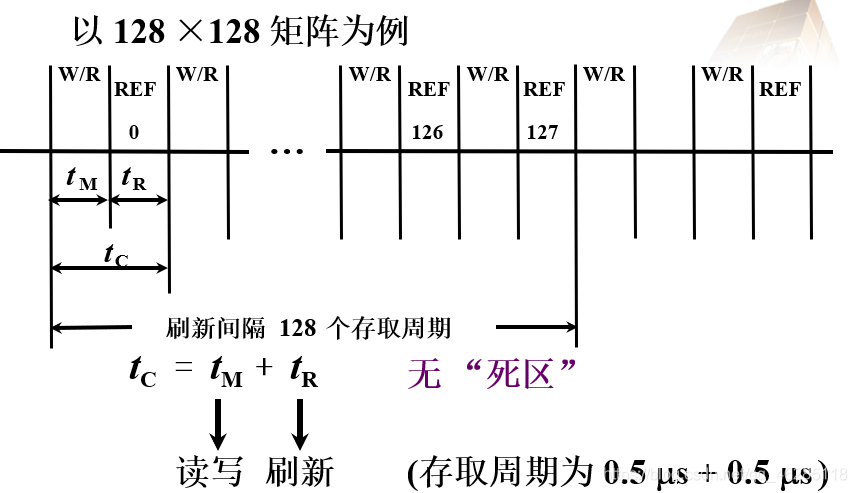

集中刷新(存取周期为0.5us):

死区:0.5us×128=64us

“死时间率”:128/4000×100%=3.2%

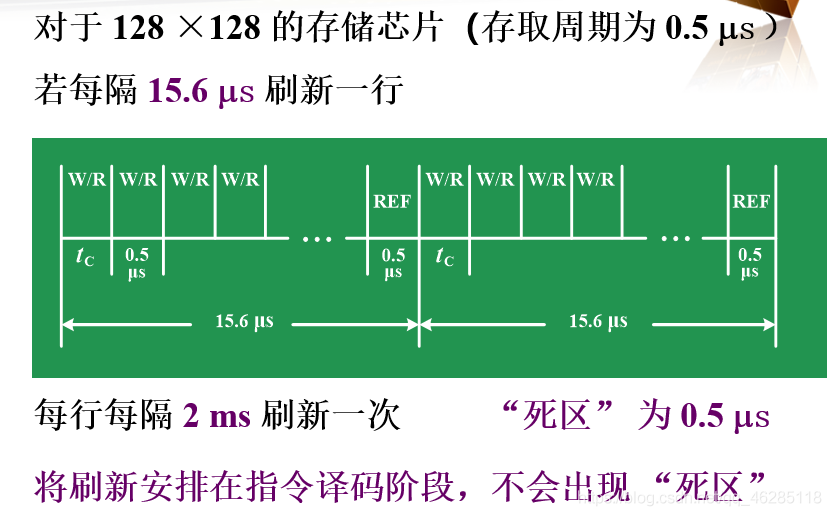

?分散刷新(存取周期为1us)

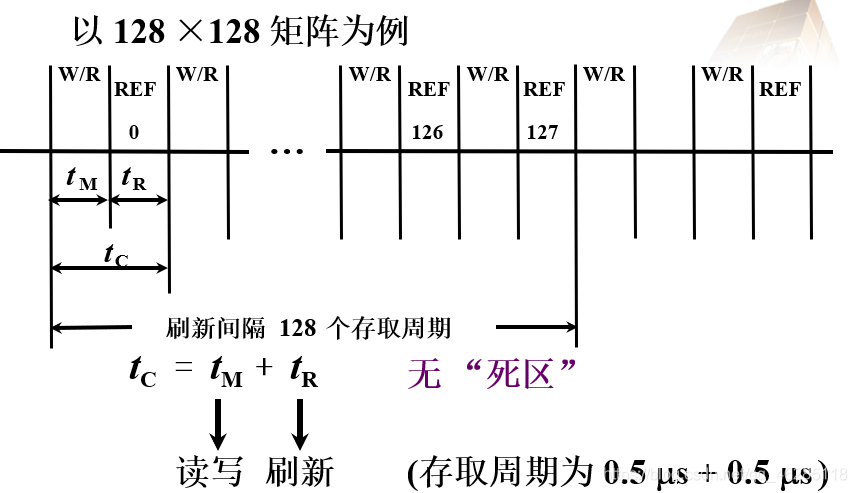

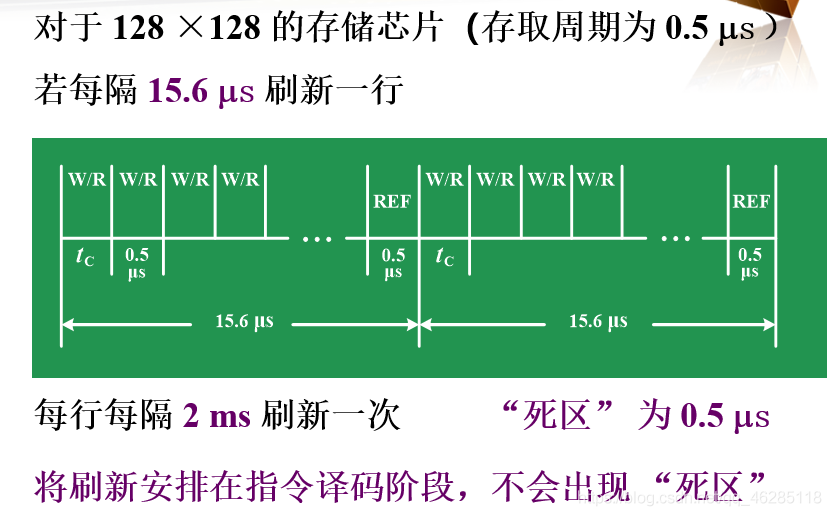

异步刷新(存取周期为0.5us):?

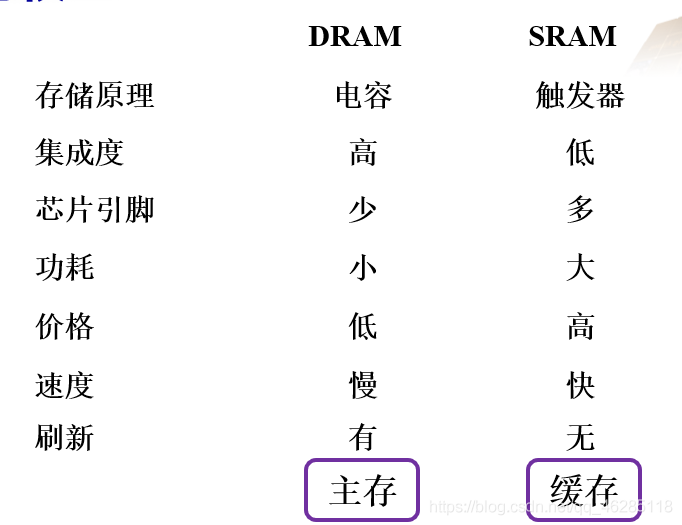

静态RAM和动态RAM的比较:?

(6)只读存储器ROM

掩膜ROM(MROM)

行列选择线交叉处有MOS管为“1”,无MOS管为“0”.

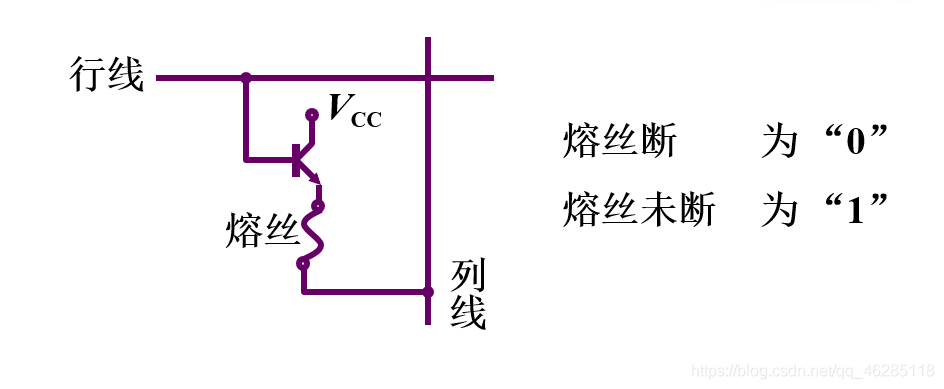

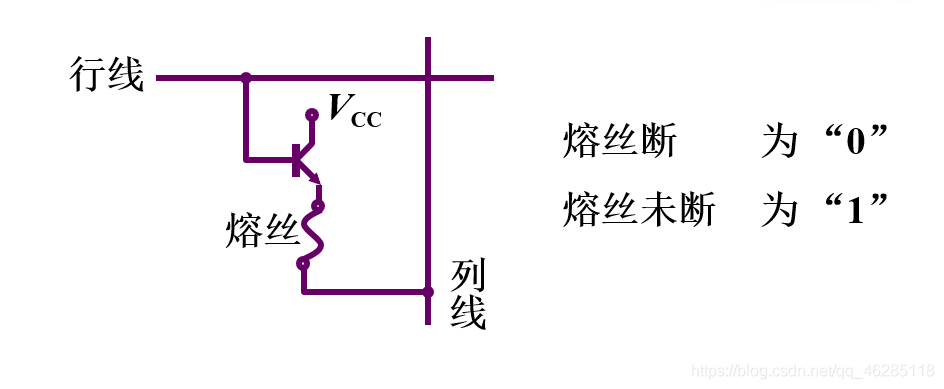

PROM(一次性编程)

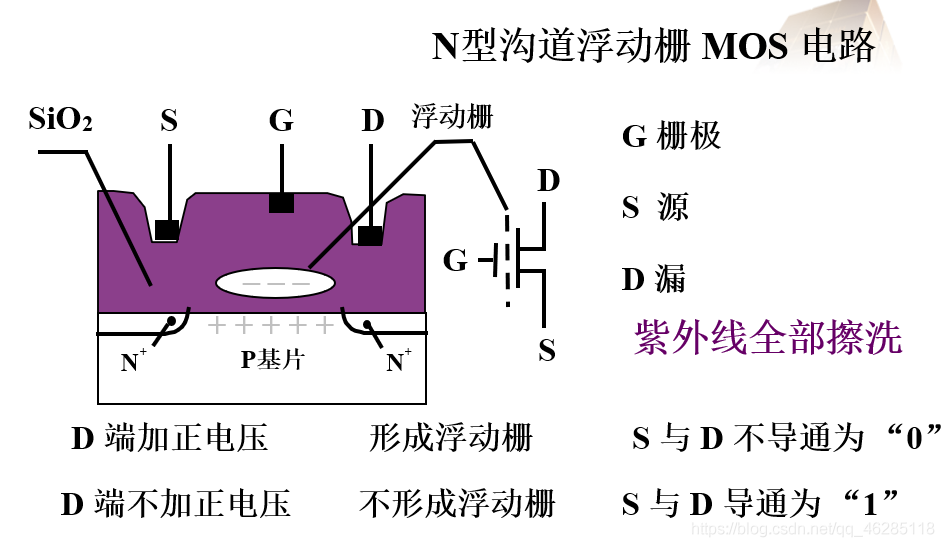

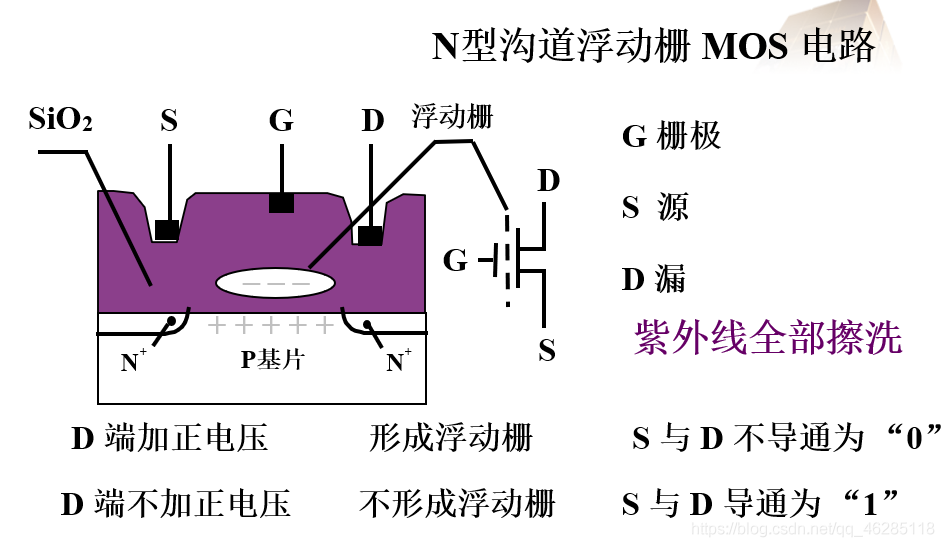

EPROM(多次编程)

Flash Memory(闪速型存储器)?

?它是在EPROM和EEPROM工艺基础上产生的一种新型的、具有性能价格比更好、可靠性更高的可擦写非易失性存储器。

(7)存储器与CPU的连接

由于单片存储芯片的容量总是有限的,很难满足实际的需求。因此,必须将若干存储芯片连在一起才能组成足够容量的存储器,称为存储容量的扩展。

通常有位扩展和字扩展。

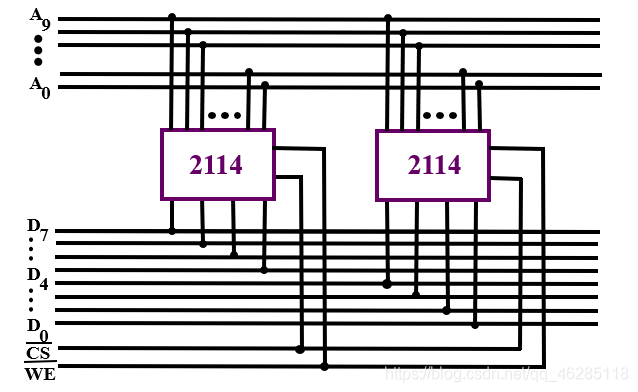

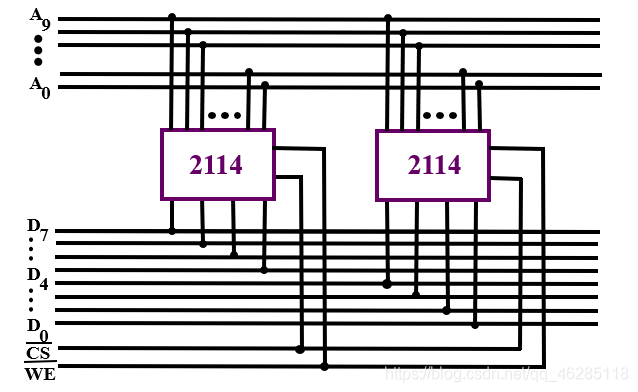

位扩展:位扩展是增加存储字长,例如2片1K×4位的芯片可以组成1K×8位的存储器。

地址线为10根,数据线为8根

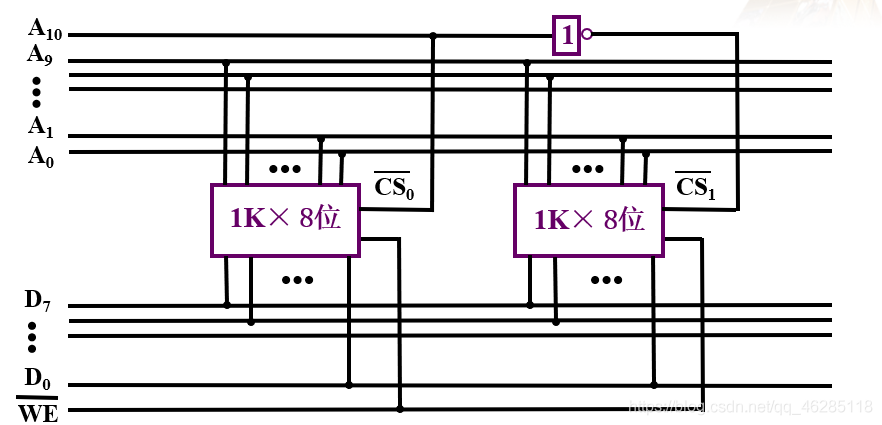

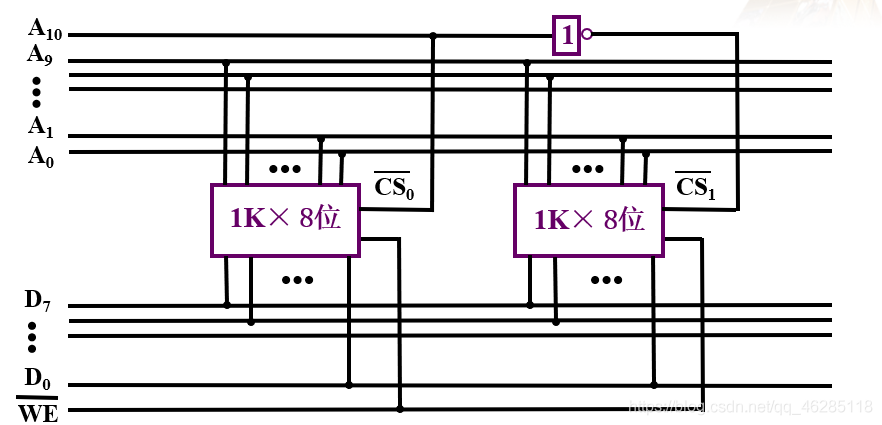

?字扩展:字扩展是增加存储器字的数量,例如用2片1K×8位的存储芯片可组成1个2K×8位的存储器,即存储字增加了一倍。

字、位扩展: 既增加存储字长又增加存储字的数量。例如用8片1K×4位组成4K×8位。

存储器与CPU连接步骤:

1.芯片选型2.地址线3.数据线4.读写命令线5.片选6.其他实际问题:时序、负载......

例题:

例4.1 设CPU有16根地址线、8根数据线,并用 作为访存控制信号(低电平有效),用

作为访存控制信号(低电平有效),用 ?作为读/写控制信号(高电平为读、低电平为写)。

?作为读/写控制信号(高电平为读、低电平为写)。

现有下列存储芯片:1K×4位RAM、 4K×8位RAM、 8K×8位RAM、 2K×8位ROM、 4K×8位ROM、 8K×8位ROM及74138译码器和各种门电路,如图4.36所示。画出CPU与存储器的连接图,要求如下:

①

主存地址空间分配:

6000H~67FFH

为系统程序区;

6800H~6BFFH

为用户程序区。cs

二、主存储器

二、主存储器

(4)半导体存储芯片简介

(4)半导体存储芯片简介