目录

1.内存接口概念

2.不同位宽设备的连接

3.时序图分析示例

1.内存接口概念

? ? ? ? GPIO和协议类接口:我们在配置GPIO或者协议类接口(uart I2C总线)时,对于CPU 来说,它不关心这些接口,它只是去操作这些寄存器,CPU通过配置相应的寄存器,然后由GPIO控制器或uart控制器发出特定的波形,CPU是根据地址去选择不同的寄存器,cpu配置寄存器时是通过内存控制器去配置的,cpu把地址发送给内存控制器, 然后由内存控制器根据地址去选择不同的模块,然后把数据发送给模块或者从模块中读取数据。CPU发出的数据并不会直接输出到外部接口,cpu只是把数据发送给了相应的寄存器。

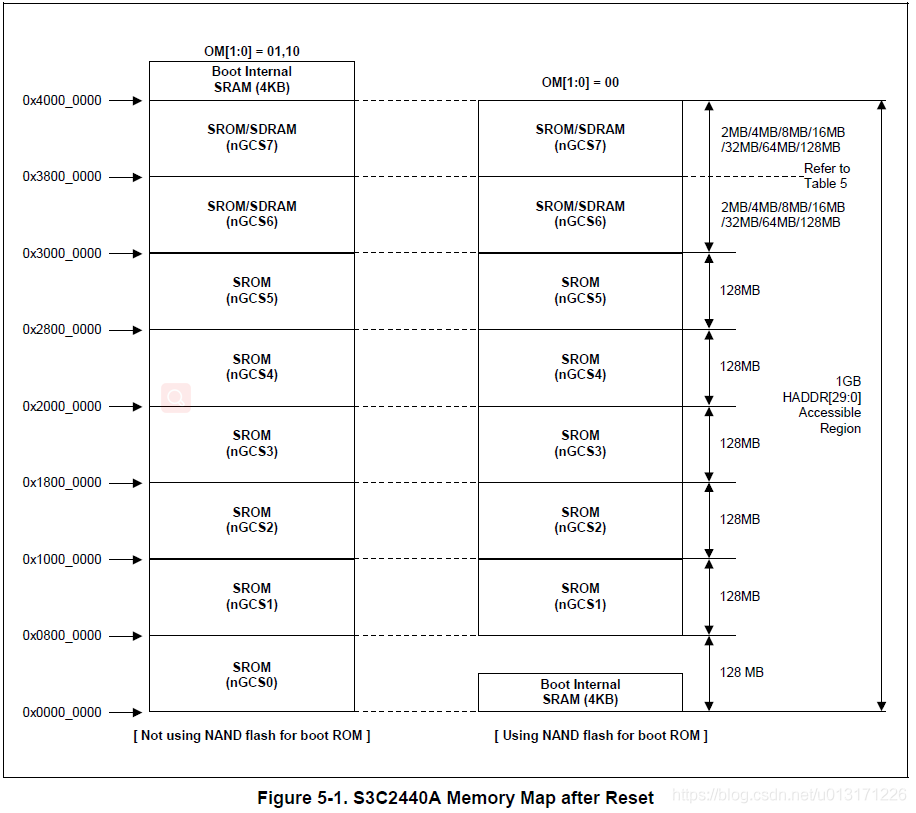

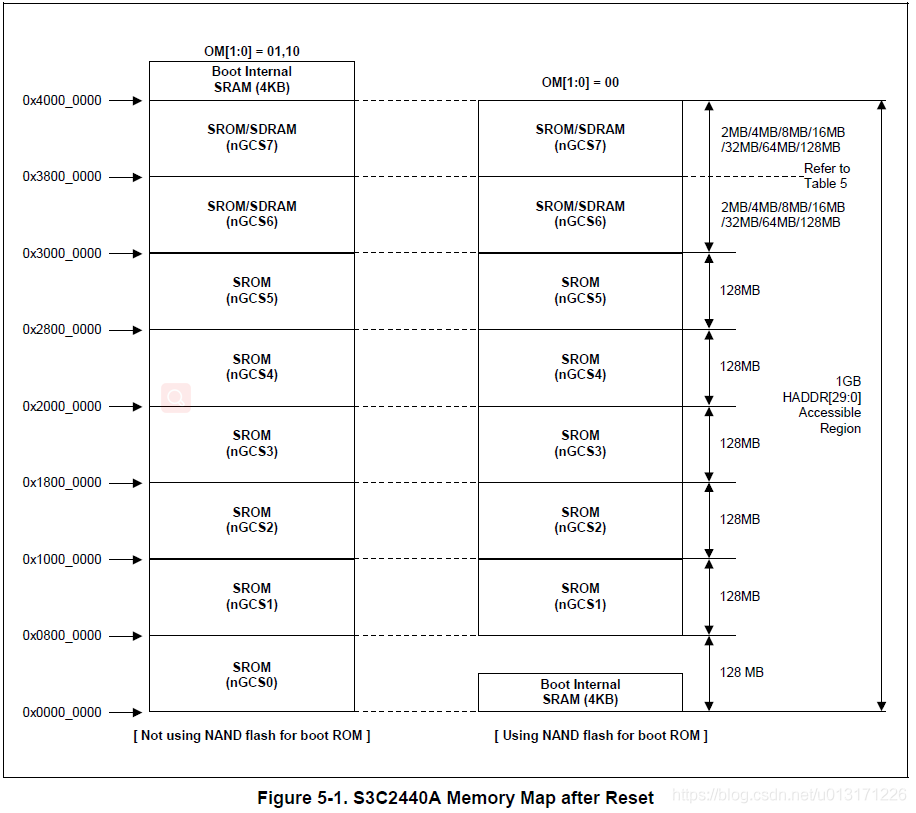

? ? ? ? 内存接口:对于内存设备来说,CPU发出的地址可以直接传给内存类设备,内存类设备包括norfalsh, 网卡,SDRAM,但是nandflash不属于内存类设备,对于内存类设备,我们cpu的数据总线和地址总线都是直接连接到内存类设备上的,然后我们的norfalsh,网卡,以及SDRAM是公用地址总线和数据总线的,我们需要用片选引脚来保证三个内存类设备在共用地址总线和数据总线的时候互不干扰, 当cpu发出地址时,内存控制器根据不同的地址范围产生不同的片选信号,从而选择不同的内存类设备,不同地址范围对应的片选引脚如下图所示,每一个片选信号可以选择的地址空间是128M。128M=2的27次方,至少需要A0 ....?A2627根地址线,但是我们一直都说我们的CPU是32位的,为什么我们只用到了27条地址线,因为我们的cpu会把32位的地址发给内存控制器,但是我们的内存控制器只使用了其中的27位。

另外,nandflash不属于cpu统一编址,nandflash的片选信号是由nandflash的控制发出来的,只有当我们的cpu访问到nandflash控制器的某个寄存器时,才会发出片选信号选中nandflash。

另外,我们应该怎么分辨数据是由CPU写给内存设备还是cpu从内存设备读取数据呢,我们使用引脚进行确定。

2.不同位宽设备的连接

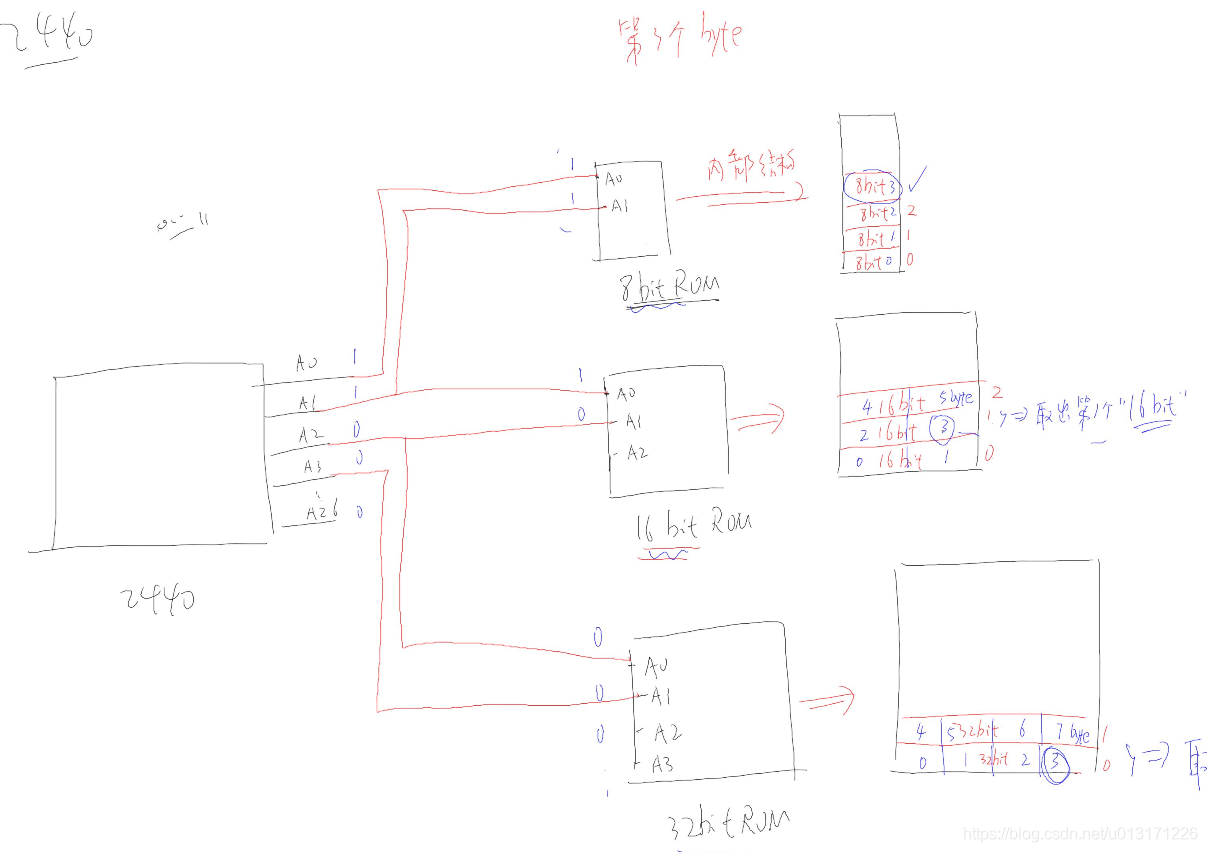

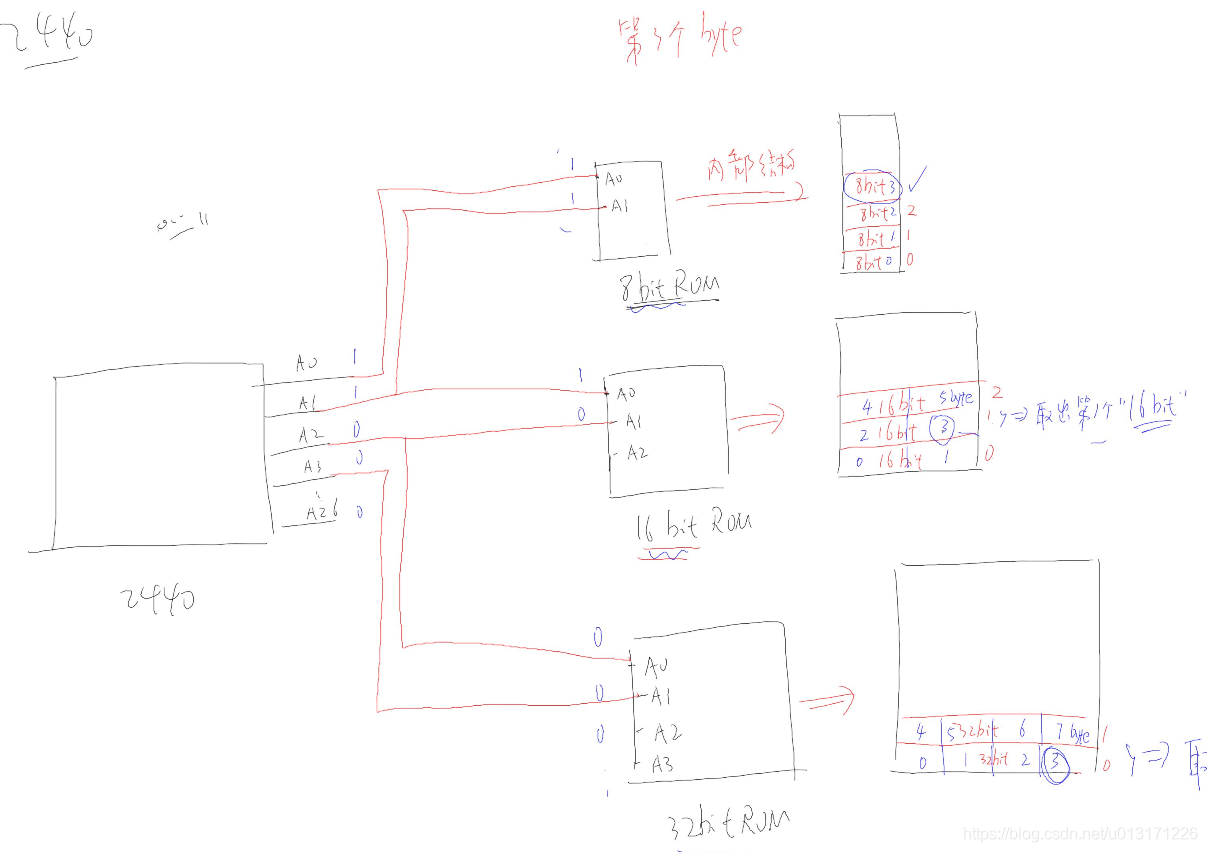

当我们外部接的是8bit的rom时,我们cpu的A0就连接rom的A0,外接的是16bit的rom时,我们cpu的A1连接rom的A0,外接的是32bit的rom时,cpu的A2连接rom的A0,具体如下

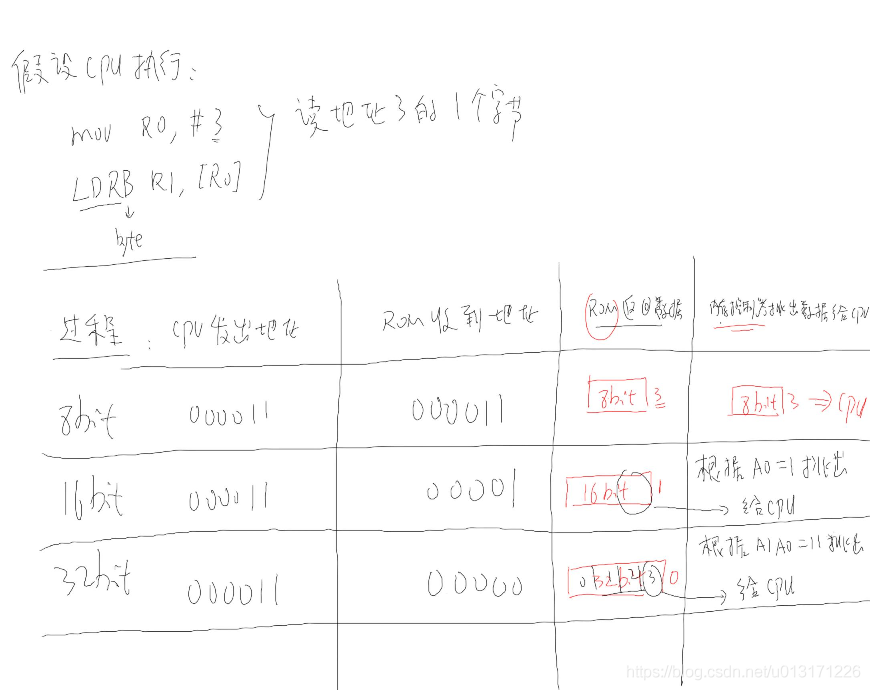

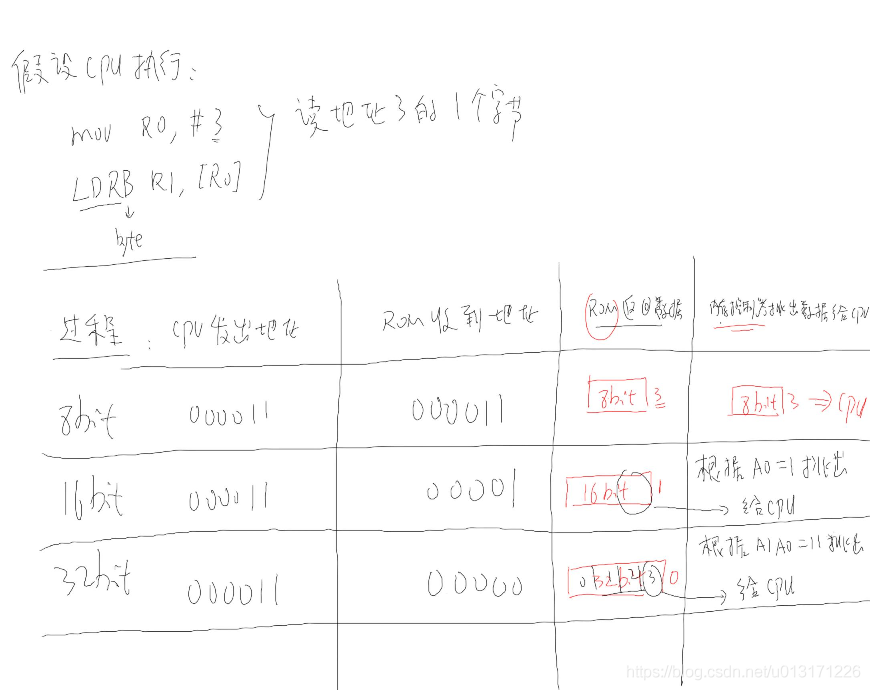

当cpu从rom读取数据时,CPU发出地质,然后rom收到地址,然后rom把数据发送给内存控制器,然后对于16bit和32bit的rom,内存控制器会从中挑出数据返回给cpu,具体如下图所示。

具体是首先根据连接到rom芯片上的地址管脚决定读取那个单元,然后根据没有连接的引脚确定从单元中取出第几个字节返回给CPU。

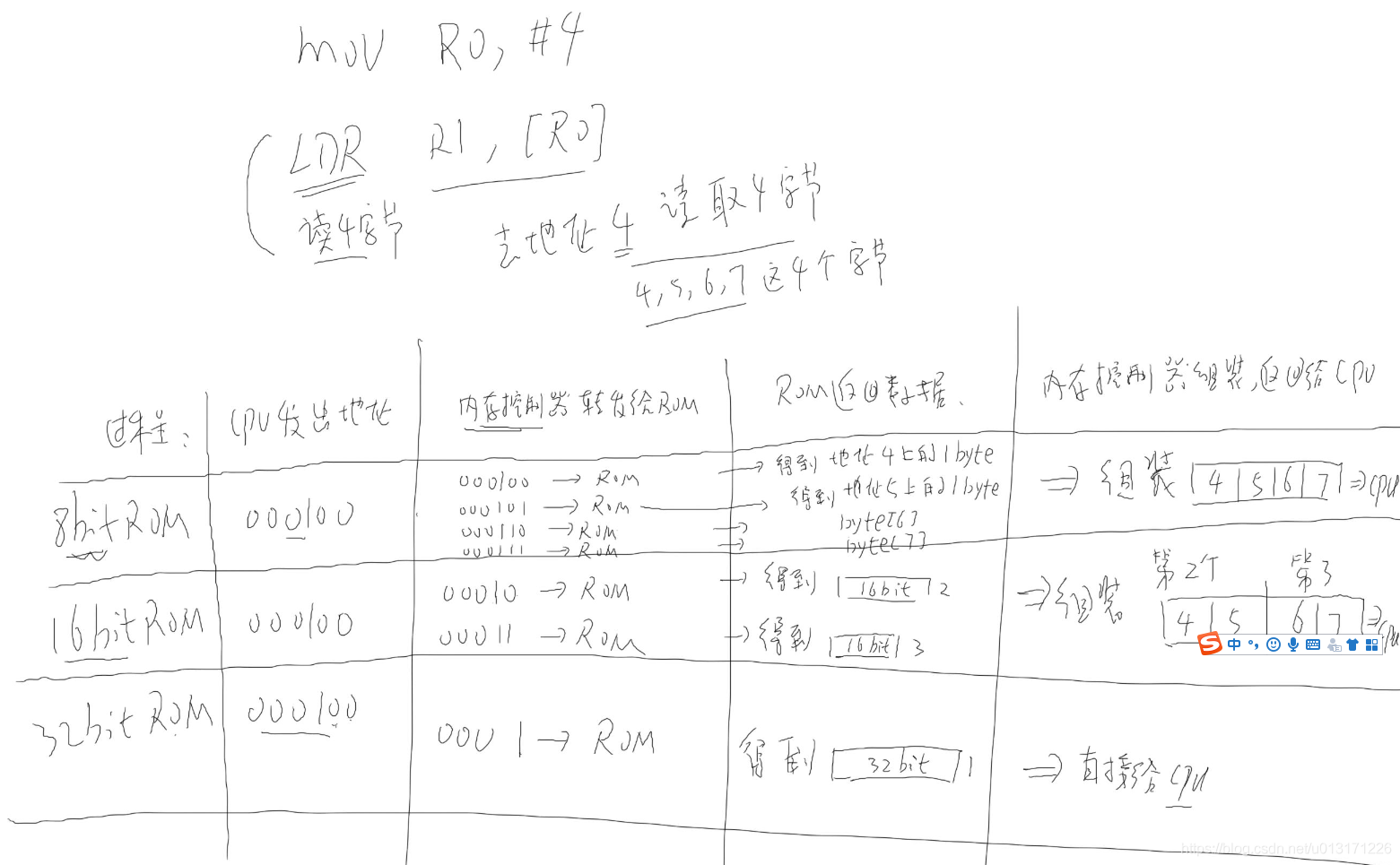

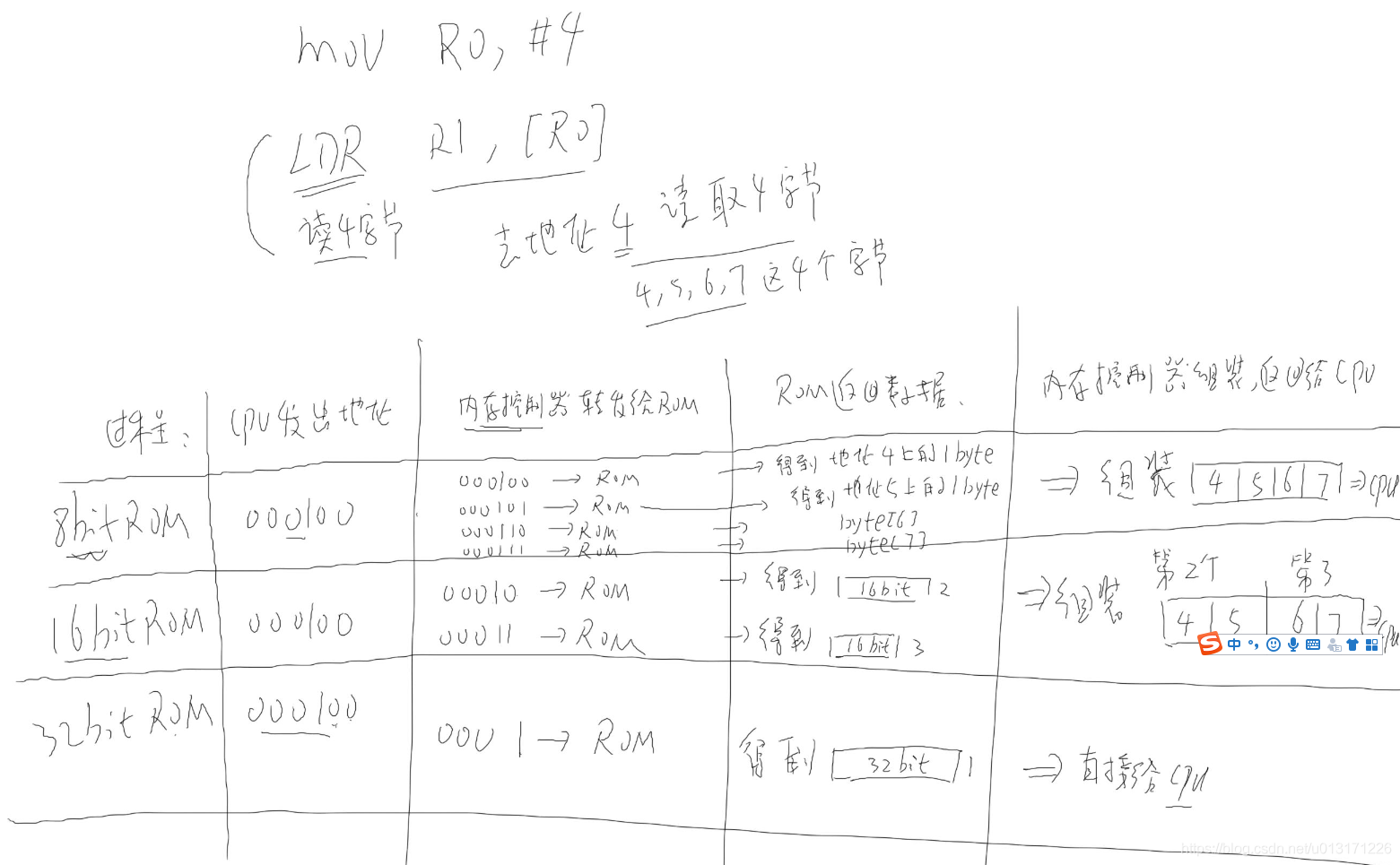

下面是另一个例子,这次我们要一次性读取四个字节,

另外,我们再访问芯片时怎么确定芯片的访问地址:1.根据片选信号确定基地址;2,再根据芯片所连接的地址线确定范围。

3.时序图分析示例

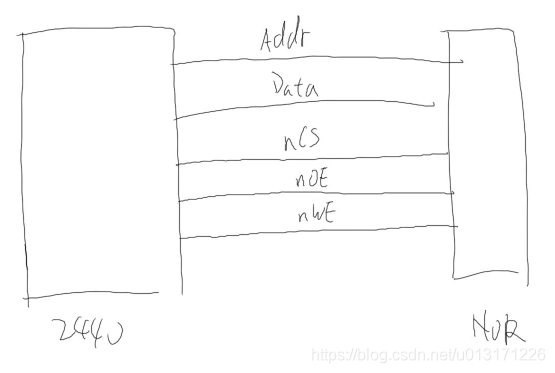

我们以norfalsh为例子讲解时序图,首先我们的cpu和norfalsh主要连接有地址线、数据线、片选信号、读信号、写信号。

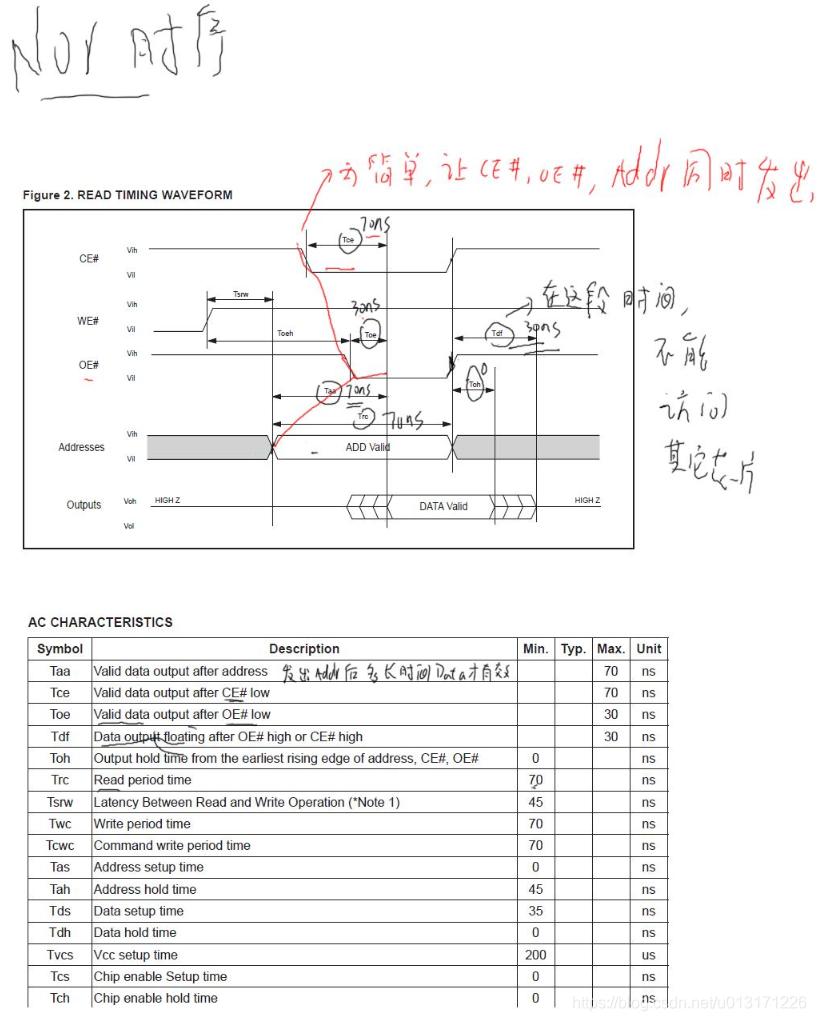

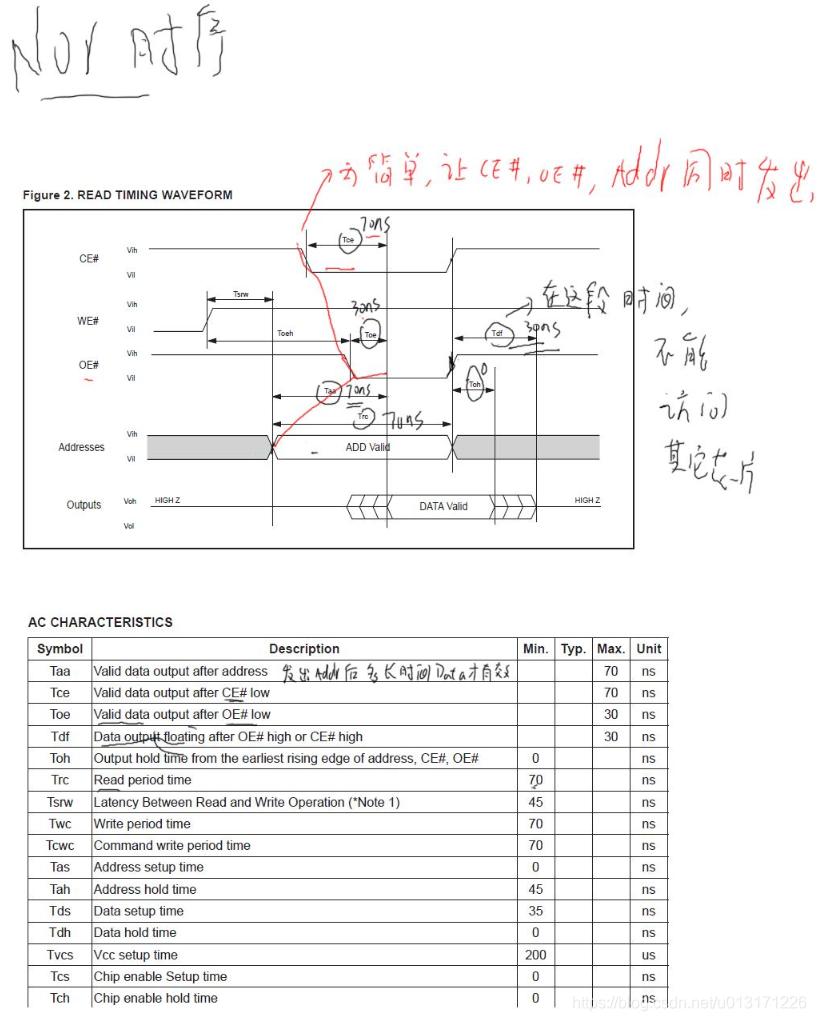

下面是norfalsh的芯片手册里面给出的norfalsh自身的时序图:

我们看一下norflash的芯片手册里面的这个表格里面的各个名称的含义,

?Taa:在cpu发出地址信号之后,过长时间之后,我这个norfalsh的数据才能给你准备好,然后最大70ns的意思是说,同一个公司生产的芯片每个芯片之间也会有点差别,有的性能好在收到地址信号之后很快就能收到数据了,但是有的性能差,在收到地址信号之后很长时间才能收到信号,但是所有的这些芯片在70ns之后肯定都能收到数据,也就是就算是最差的芯片,那么70ns之后肯定也准备好了,但是70ns之后的不能保证数据是有效的。

Tce:当发出片选信号之后,过多长时间数据才有效,

Toe:数据在 Toe信号之后多长时间有效。

Toh:数据保持时间,最小值是0,

Tdf:我们之前说过要去访问一个芯片,先选中它,但是当我访问完一个芯片,然后片选信号释放之后,你不能立刻去访问另一个芯片,因为当前芯片片选刚被释放之后,数据线的状态还不稳定,还不是高阻状态,实际上这个值一般我们不需要理会,假设我们刚访问完这个norflash,数据还没有到高阻状态,需要等待30ns, 但是这个时候如果我再立刻开始访问这个norflash,你首先要发送片选以及地址信号,然后等待70ns才会接收数据,等到了70ns,这里的数据线早就恢复到高阻状态了,就可以访问了。

我们在访问norflash的时候,为了简单,我们把片选信号,读信号,地址信号三个同时发出。

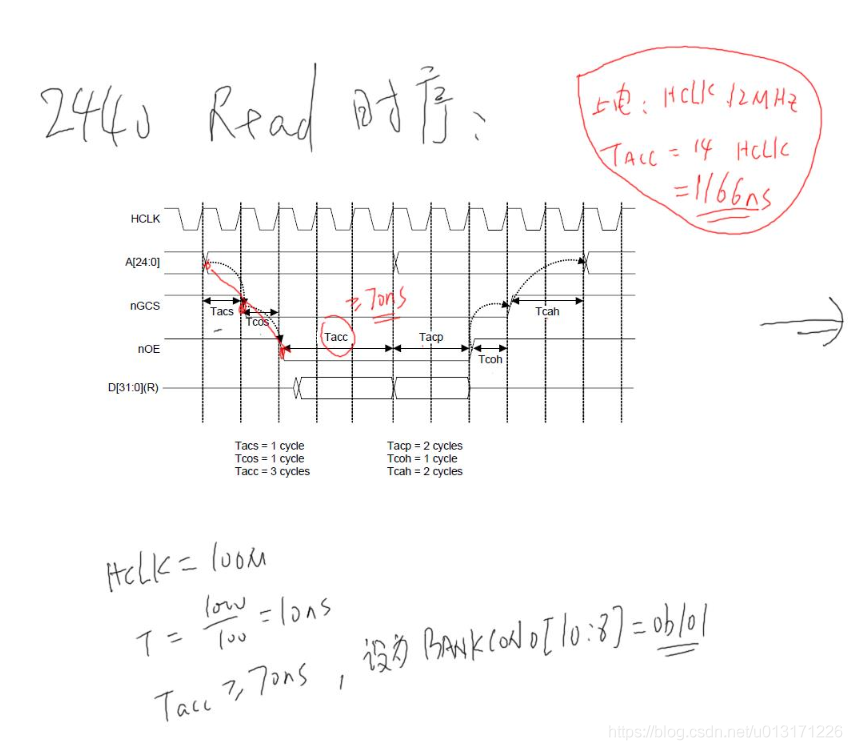

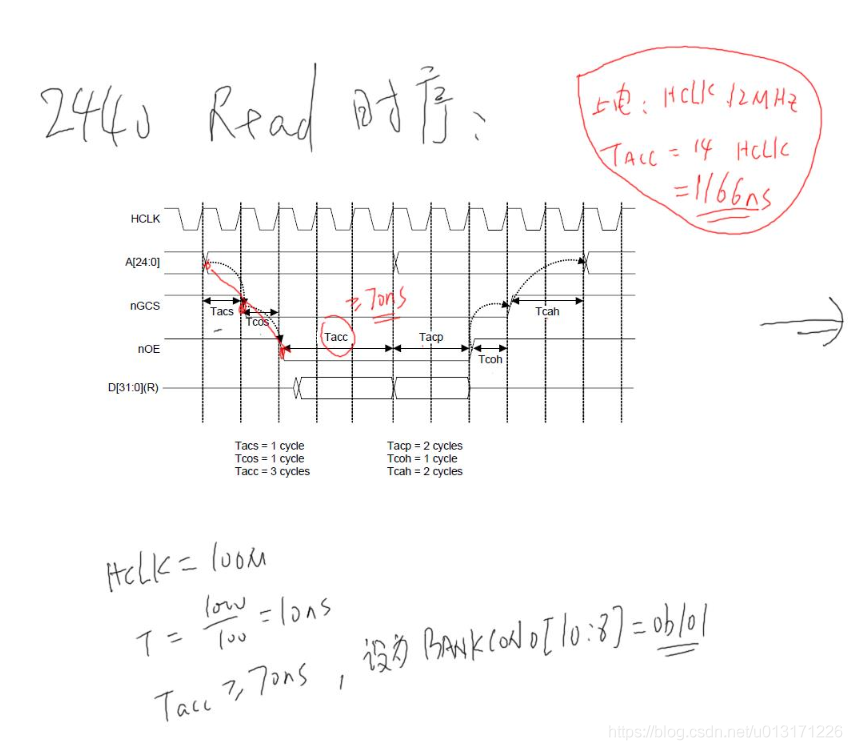

下面我们看一下怎么设置S3C2440,S3C2440读取norfalsh的时序图如下:

我们在芯片手册里面搜索Tacc,找到BANK CONTROL REGISTER,由于我们的norfalsh是连接到bank0上面,所以我们设置BANKCON0寄存器,我们可以看到这个寄存器的Tacc位的默认值是111,是14个时钟周期,板子刚开始上电的时候时钟周期是12M,Tacc是14个时钟周期是1166ns,所以我们一上电的时候,使用最保险的参数,可以访问各种不同性能的norflash。

假设HCLK是100M,那么时钟周期是10ns,那么我们设置Tacc是8个时钟即可。

接下来看一下访问norflash还有哪些寄存器需要设置。

cs